Guest Blogger Sanjay Gangal

Sanjay Gangal is a veteran of Electronics Design industry with over 25 years experience. He has previously worked at Mentor Graphics, Meta Software and Sun Microsystems. He has been contributing to EDACafe since 1999. Intel Foundry Unveils Breakthroughs in Transistor and Packaging Technologies at IEDM 2024December 17th, 2024 by Sanjay Gangal

At the IEEE International Electron Devices Meeting (IEDM) 2024, Intel Foundry unveiled a series of pioneering advancements poised to reshape the semiconductor landscape for the coming decade. With innovations addressing transistor scaling, interconnect efficiency, and advanced packaging, Intel’s research highlights the company’s leadership in enabling the exponential growth of computing power required to meet artificial intelligence’s (AI) insatiable demands. As AI continues to push the limits of existing technology, the need for energy-efficient, high-performance chips grows ever more critical. Intel’s latest breakthroughs mark significant steps in transistor miniaturization, interconnect materials, and assembly techniques—key ingredients for sustaining Moore’s Law and advancing toward a trillion-transistor chip by 2030. “Our research at Intel Foundry is focused on overcoming the technological roadblocks of tomorrow,” said Sanjay Natarajan, Intel senior vice president and general manager of Intel Foundry Technology Research. “These advancements reflect our mission to deliver cutting-edge semiconductor innovations, developed domestically, to meet global AI demands and solidify U.S. manufacturing leadership under initiatives like the CHIPS Act.” NVIDIA’s RISC-V Transformation: How Open Architecture Became Central to AI and ComputingNovember 6th, 2024 by Sanjay Gangal

Last week at the RISC-V Summit in Santa Clara, NVIDIA’s Vice President of Multimedia Architecture/ASIC, Frans Sijstermans, took to the stage to recount NVIDIA’s strategic transformation. For an audience of engineers, developers, and industry insiders, Sijstermans’ keynote was both an inside look at NVIDIA’s journey with RISC-V and a demonstration of how open architecture has fueled rapid technological growth. Over the past seven years, NVIDIA’s adoption of RISC-V has marked a major shift in its approach to microprocessor design, from the niche Falcon core to a globally scaled RISC-V integration that now spans billions of cores.

From Falcon to RISC-V: A Strategic LeapIn 2017, Sijstermans first announced NVIDIA’s plan to phase out Falcon, their proprietary 32-bit microprocessor, and adopt RISC-V. At the time, Falcon had been used for a decade, embedded across various applications. But as computing demands grew more complex, NVIDIA recognized the need for a more adaptable, extensible architecture. After evaluating multiple architectures, the company found RISC-V’s open, customizable foundation aligned with its goals for scalability, security, and performance. “Customization is really the key here,” Sijstermans emphasized. “As Moore’s Law slows, it becomes increasingly important to use every bit of silicon effectively. RISC-V’s customizable structure allows us to design specific extensions for our applications.” This customization became one of RISC-V’s most appealing attributes for NVIDIA, which has since been able to innovate rapidly within the flexible framework the architecture provides. The Six Semiconductor: Innovating Memory Interface IP in the AI EraAugust 8th, 2024 by Sanjay Gangal

In the rapidly evolving landscape of semiconductor technology, The Six Semiconductor Inc., a subsidiary of Open Edge Technology Inc., has emerged as a significant player, particularly in the realm of high-speed memory interface intellectual property (IP). Founded by a group of seasoned engineers with deep ties to the semiconductor industry, the company is capitalizing on the growing demands of artificial intelligence (AI) to carve out a niche in a highly competitive market. Origins Rooted in ExperienceThe story of The Six Semiconductor began six years ago, when a close-knit team of engineers, all former colleagues from ATI Technologies (later absorbed by AMD), identified an opportunity in the burgeoning AI sector. At a time when AI was starting to reshape the tech industry, the founders saw an increasing demand for specialized IP to support the intensive memory needs of AI accelerators. “We recognized that the AI boom was not just a temporary trend, but a paradigm shift that required new, robust infrastructure,” said Ricky Lau, Chief Technology Officer and co-founder of The Six Semiconductor. “With our collective experience in high-speed memory interface design, we knew we could meet this need.” The company’s initial focus was on developing GDDR6 IP, which is crucial for AI processors that require vast amounts of memory bandwidth. Drawing on their deep expertise in GPU design from their days at AMD, the team was able to push the boundaries of performance, setting their IP apart from existing standards.

Read the rest of The Six Semiconductor: Innovating Memory Interface IP in the AI Era Streamline 3D IC verification with a shift-left strategyJune 13th, 2024 by Sanjay Gangal

Unlike traditional integrated circuit (IC) designs, multi-dimensional 2.5D and 3D ICs are composed of multiple individual chiplets, each built to a separate process node best suited for its specific purpose. There are many different design options for connecting these chiplets, and any or all of these approaches can be combined on a single 3D IC assembly. This results in multiple components of different materials integrated in all three dimensions, which creates new and unique verification challenges for 2.5/3D IC designers. 3D IC assembly flow Multi-dimensional ICs are one part of the industry’s answer to moving beyond the limits of Moore’s law. While 2.5D approaches, particularly chiplets placed upon a silicon interposer, have gained broad adoption, the move to true 3D IC is still early in its design lifecycle. Design tools and best design practices continue to evolve and improve, but many challenges are yet to be resolved. In a true 3D IC, early design and package planning can be a challenging task, as the specific approach, materials, and chiplet placements used will induce thermal and mechanical stresses that can impact the intended electrical behavior of the full assembly design (Figure 1). Selecting the optimal approach and optimal chiplet placements becomes critical, implying multiple iterations will be required to determine the best final design. Read the rest of Streamline 3D IC verification with a shift-left strategy Winning doesn’t happen at the finish line, even in IC verificationFebruary 19th, 2024 by David Abercrombie

By David AbercrombieIn motor car racing, many people think the win happens on the track, with lightning-fast pit stops ensuring the fastest car takes the black and white checkered flag at the finish line. In reality, the win happened long ago, in the garage, as the car was built and tested and rebuilt. The same is true in integrated circuit (IC) design. Getting a design through a successful tapeout on schedule isn’t just the result of signoff verification. It begins much earlier, back in the design and implementation stages. Finding and correcting critical errors in these early design stages helps design teams make adjustments quickly while layouts are still more open and flexible, avoiding time-consuming and complex fixes during signoff that can play havoc with delivery schedules. But what happens when that early verification doesn’t match signoff verification? Despite all the work designers put in during the design stages, they may find themselves still trying to fix those hard errors, only now they’re constrained by layout restrictions, and under the gun to meet the schedule. Calibre® shift left (early design-stage) solutions bring industry-leading Calibre signoff-quality verification and design optimization into the design and implementation environments. Shift left verification and optimization can help design teams minimize those late-stage signoff iterations while still delivering high performance, high reliability designs. Using the same qualified rule decks and underlying engines used by the signoff toolsuite, Calibre shift left tools and technology deliver targeted verification that hones in on those errors most critical in early-stage designs, provide thorough analysis of complex design constraints, support designers with guided debugging to enable optimal fixes that remain signoff-compliant throughout the design flow, and apply selective automated design optimizations, all within a user-friendly toolset integrated into the designer’s design or implementation environment. Read the rest of Winning doesn’t happen at the finish line, even in IC verification Unveiling Apple’s Game-Changing MacBook Pro with M3 ChipsOctober 31st, 2023 by Sanjay Gangal

Apple has once again pushed the boundaries of innovation with the launch of its latest MacBook Pro lineup. Featuring the all-new M3 family of chips, including the M3, M3 Pro, and M3 Max, these laptops promise to deliver unprecedented performance and capabilities. From students to creatives, coders to machine learning programmers, Apple’s new MacBook Pro is set to revolutionize the way we work and play. In this article, we will dive deep into the details of this groundbreaking release, explore the capabilities of the M3 family of chips, and discuss how these laptops cater to a wide range of users.  MacBook Pro with M3 enables users to compile and test millions of lines of code in Xcode with even greater speed. The M3 Family of Chips Apple’s M3 family of chips represents a monumental leap in silicon technology. These chips are the first to utilize the industry-leading 3-nanometer technology, promising faster and more efficient performance. The GPU architecture in these chips is a game-changer, thanks to a groundbreaking technology called Dynamic Caching. This innovation allocates local memory in hardware in real time, optimizing memory usage for each task. The result is a dramatic increase in GPU utilization and performance, especially in resource-intensive applications and games. Additionally, the M3 chips introduce new rendering features, such as hardware-accelerated mesh shading and ray tracing, which were previously unavailable on Mac. These features enhance the visual complexity and realism of scenes in games and other applications. Read the rest of Unveiling Apple’s Game-Changing MacBook Pro with M3 Chips The value of a shift left strategy in IC designSeptember 1st, 2023 by Sanjay Gangal

By David Abercrombie and Michael White No matter what process node you’re working at, or how big or how complex your integrated circuit (IC) design is, design enablement is a complex process that goes through multiple stages. The faster you get your design to market, the better your chances of achieving your market goals. But getting your design to the foundry on schedule, while ensuring the final product will not only be manufacturable, but also provide the intended performance and reliability, all depends on achieving and maintaining high productivity and quality of results throughout the design flow. IC design companies, like any other business, constantly look for ways to improve and speed up their processes. One approach that has recently gained significant traction is the idea of “shifting left”—performing design layout verification and optimization earlier in the design flow, instead of waiting until the signoff verification stage. However, simply shifting signoff physical verification to earlier stages of the design flow is neither practical nor productive. Signoff verification is intended to apply to full chip designs where all components are complete and connected. Running signoff verification on incomplete or “dirty” designs is not only time-consuming, but also returns millions of errors, many of which are irrelevant, as they are caused by the incomplete nature of the layout. Hardly the increase in productivity the design companies were hoping for. Read the rest of The value of a shift left strategy in IC design IBM Research’s latest analog AI chip for deep learning inferenceAugust 22nd, 2023 by Sanjay Gangal

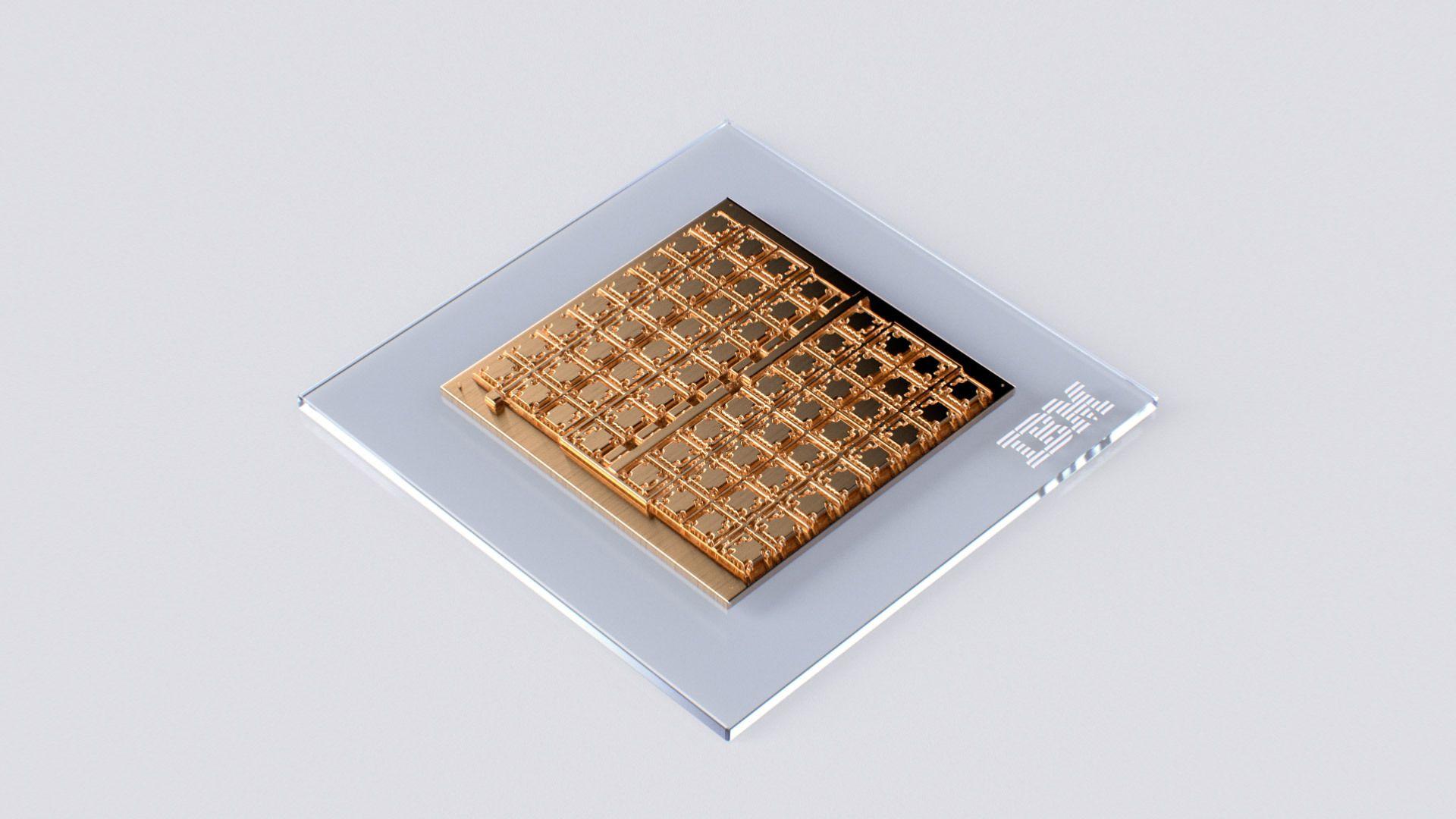

By: Abu Sebastian, Manuel Le Gallo-Bourdeau, Vijay Narayanan The energy-efficient chip showcases critical building blocks of a scalable mixed-signal architecture. A rendering of IBM’s analog AI chip. We’re just at the beginning of an AI revolution that will redefine how we live and work. In particular, deep neural networks (DNNs) have revolutionized the field of AI and are increasingly gaining prominence with the advent of foundation models and generative AI. But running these models on traditional digital computing architectures limits their achievable performance and energy efficiency. There has been progress in developing hardware specifically for AI inference, but many of these architectures physically split the memory and processing units. This means the AI models are typically stored in a discrete memory location, and computational tasks require constantly shuffling data between the memory and processing units. This process slows down computation and limits the maximum achievable energy efficiency. EDACafe Industry Predictions for 2023 – ThaliaFebruary 1st, 2023 by Sanjay Gangal

By Sowmyan Rajagopalan, CEO, Thalia Design AutomationThe economic outlook for semiconductor industry in 2023 Since the start of the Covid-19 pandemic in 2020, the global market for semiconductors has not looked very stable. It has made long-term planning tough if not impossible. A forecast fall then turned into a rapid growth, followed by an oversupply problem with excess inventories. In 2021, more than $0.5 trillion units were shipped, which was a record, and represented a significant 26.2% growth in value over 2020. That growth continued into 2022, with semiconductor industry growing at 7.3%. So what’s coming further down the track? Due to an oversupply issue and slower demand in consumer electronics, Gartner’s forecast for 2023 is a small decline in the market by 2.5%. Even with that modest decline, we are still looking at a staggering $620 billion semiconductor market this year. However, the market for automotive electronics continues to evolve to support the rapidly increasing volume of devices in the modern vehicle: from non-critical systems in audio, video, satellite navigation and connectivity devices, to fundamental systems in battery control, and mission critical Advanced Driver Assistance Systems (ADAS) and monitoring systems. Although analysts’ numbers differ, the forecasts for the growth of automotive electronics all show a similar and definite upward trajectory. The automotive industry could be a driving force for the industry – potentially leading the direction of consumer electronics with the largest tier one companies sourcing directly from foundries: changing the power balance and upsetting the decades-old structure of a tiered supply chain in automotive manufacturing. Read the rest of EDACafe Industry Predictions for 2023 – Thalia EDACafe Industry Predictions for 2023 – AvishtechJanuary 31st, 2023 by Sanjay Gangal

By Kella Knack, Senior Director of Strategic Marketing, Avishtech2023: The Year of Refining the Role of EDA Toolsets One year ago, as an industry as well as a country and world, we were dealing with the remnants of COVID-19 and its resultant effects on business. Those efforts centered on a variety of global issues—fabrication facilities having limited manufacturing staffs and production capabilities; “rolling” shut downs of various facilities; materials shortages; shipping capabilities and cost, and most impactful, the global chip shortage. The “Sort of” Cloudy Crystal Ball for ‘23 As we move towards the end of 2022 and the beginning of 2023, we are still challenged by on-going global chip shortages. And, there are also two more significant wrinkles:

There are some silver linings resulting from the foregoing: new defense contracts the likes of which we have not seen in a long time and U.S.-based chip manufacturing operations that will help to address the global chip shortage and relieve our strong dependency on Taiwanese manufacturing operations. Read the rest of EDACafe Industry Predictions for 2023 – Avishtech |

|

|

|||||

|

|

|||||

|

|||||