EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. AI calling for new fabs; EDA updates; workload-aware AVS; China’s Risc-V activity; Renesas adding GaN capabilityJanuary 25th, 2024 by Roberto Frazzoli

Artificial Intelligence keeps creating “circles” – that is, producing consequences that feedback on AI itself, further amplifying its impact. Besides the well-known chip performance “virtuous circle” (powerful processors enabling AI, and AI enabling even more powerful processors), another circle is looming – virtuous or vicious, depending on the point of view. It can be described as follows: chip fabs capacity enables the construction of large datacenters, and the success of AI applications fueled by large datacenters generates the demand for even larger fab capacity. Clearly, this insatiable hunger for GPUs is “virtuous” from the point of view of semiconductor sales, but can be considered “vicious” from an energy consumption standpoint. According to a CB Insights estimate, in 2024 three million operational H100 Nvidia chips – in datacenters around the world – will collectively consume almost 14 GWh, more than the whole Guatemala state (13 GWh). Sam Altman reportedly looking to spur the construction of new fabs According to two press reports (here and here), OpenAI’s CEO Sam Altman is trying to launch a network of new fabs to ensure his company an abundant supply of GPUs and reduce its reliance on Nvidia. Reportedly, Altman has been discussing the project with investors from United Arab Emirates and Japan’s SoftBank Group – as well as with potential foundry partners like TSMC, Intel and Samsung. OpenAI would be the new fabs’ primary customer. “Big tech” companies are the biggest buyers of Nvidia’s H100 GPUs. In a Thread post (quoted by Reuters), Mark Zuckerberg recently wrote “We’re building a massive amount of infrastructure. At the end of this year, we’ll have ~350k Nvidia H100s — and overall ~600k H100 equivalents of compute if you include other GPUs”. Synopsys to acquire Ansys: what will be the impact on the EDA industry?January 18th, 2024 by Roberto Frazzoli

Is the $35 billion deal going to change the EDA oligopoly? Is the need for better electronics-physics integration a game changer? Is EDA as a standalone industry gradually disappearing? Will Cadence look for merger opportunities? The rumors have been confirmed: after a seven-year partnership, on January 16th Synopsys and Ansys announced that they have entered into a definitive agreement under which Synopsys will acquire Ansys for an enterprise value of approximately $35 billion. The transaction is anticipated to close in the first half of 2025. Summing up Synopsys’ 2023 revenue (approximately $6 billion) and Ansys’ 2023 revenue guidance (approximately $2 billion), the combined entity is expected to achieve a $8 billion annual income. According to the two companies, this merger is motivated by a compelling rationale: first of all, the new customer demands stemming from the complexity of today’s intelligent systems (including the chiplet trend), which require the integration of semiconductor design and simulation and analysis, in a “silicon to systems” approach that fuses electronics and physics; besides that, new growth opportunities in areas such as automotive, aerospace and industrial, where Ansys has an established presence; and the complementarity of the two companies’ respective solutions. A key role in the integration of the two organizations will be played by Rick Mahoney, currently Chief Revenue Officer in the Go-to-Market Group at Synopsys and previously Senior Vice President of Worldwide Sales, Customer Excellence, and Marketing at Ansys. Read the rest of Synopsys to acquire Ansys: what will be the impact on the EDA industry? Synopsys to reportedly buy Ansys; automotive alliances; more IEDM innovations; epitaxial grapheneJanuary 11th, 2024 by Roberto Frazzoli

As the company announced with a post on X (Twitter), “Intel Oregon welcomes major components of ASML first shipped High-NA EUV technology to help enable the continued and relentless pursuit of Moore’s Law.” Is this new piece of equipment going to help Intel advance its “5 nodes in 4 years” program? According to SemiAnalysis, double patterning with the “traditional” EUV litho equipment (low numerical aperture) is still a better option – in terms of cost and throughput – than single patterning with the new high numerical aperture litho equipment. Let’s now move to more news, catching up on some of the updates from the last thirty days or so. Synopsys to reportedly buy Ansys It looks like the EDA oligopoly is bound to always be restricted to just three big companies. According to a January 5 report from The Wall Street Journal, Synopsys is in advanced talks to acquire Ansys for around $35 billion in a stock-and-cash deal. Reportedly, the two companies are now in exclusive negotiations. Rumors started with a December 22 Reuters exclusive report revealing that Synopsys had submitted an offer to acquire multiphysics simulation specialist Ansys. While the acquisition of Ansys would be a transformative event for Synopsys, there’s no doubt that the company co-founded by Aart de Geus has a long track record of acquiring other EDA players: just take a look at this list. 2023 Year in ReviewJanuary 1st, 2024 by Roberto Frazzoli

Let’s finish the year with a quick recap of some of 2023 events and trends. New fab announcements Geopolitical tensions continued throughout the year, prompting governments around the world to pass new subsidies – after the ones approved in 2022 – to support their respective semiconductor industries. Among them, the European Commission launched an €8.1 billion “Important Project of Common European Interest” on microelectronics; Japan is expected to invest $13 billion on semiconductors; and South Korea passed a “K Chips Act” tax credit plan. The subsidies launched in 2022 – such as the US Chips Act and its European counterpart – spurred several new fab announcements in 2023: a partial list includes a Wolfspeed wafer fab in Saarland, Germany; a Texas Instruments wafer fab in Lehi, Utah; the expansion of an existing Microchip facility in Colorado Springs; a new capital injection to TSMC Arizona; an Infineon plant for analog/mixed-signal technologies and power semiconductors in Dresden, Germany; the choice of Chitose, Japan, as the site for the first Rapidus fab; the expansion of Applied Materials’ campus in Silicon Valley to build the “Equipment and Process Innovation and Commercialization” Center; the expansion of Analog Devices’ European headquarters in Limerick, Ireland, to build a new R&D and manufacturing facility; a joint STMicroelectronics-GlobalFoundries fab in Crolles, France; Intel factories in Kiryat Gat, Israel, and in Wrocław, Poland; Broadcom investments in Spain to build back-end semiconductors facilities; a CEA-Leti FD-SOI fab in Grenoble; the expansion of Analog Devices’ wafer fab in Beaverton, Oregon; a Silicon Box packaging facility in Singapore; the expansion of Infineon’s Kulim, Malaysia, SiC fab; a joint investment from TSMC, Bosch, Infineon and NXP on “European Semiconductor Manufacturing Company”, to be based in Dresden, Germany; an Amkor packaging and test facility in Peoria, Arizona. This is a list of announcements; real fabs will obviously take years to complete. AMD’s new AI accelerators; edge AI updates; microLED advancements; funding to private semi firmsDecember 11th, 2023 by Roberto Frazzoli

Artificial intelligence takes center stage this week, with announcements from AMD, some edge AI news and the introduction of Gemini. Among other updates, the recent funding increase to private semiconductor firms. AMD MI300 to challenge Nvidia H100 At the recent “Advancing AI” event, AMD has launched multiple new AI products, including the Instinct MI300 Series data center AI accelerators, ROCm 6 open software stack, and Ryzen 8040 Series processors with Ryzen AI. The event was intended to showcase growing momentum for AMD-powered AI solutions, particularly in data centers; on the occasion Microsoft, Dell Technologies, HPE, Lenovo, Meta, Oracle, Supermicro and others announced their adoption of the new AMD Instinct MI300X and MI300A data center AI accelerators for training and inference solutions. Analysis website SemiAnalysis has provided a benchmark-by-benchmark comparison of AMD MI300 performance versus Nvidia H100 GPU, highlighting that some AMD results only apply to the “forward pass” processing step. However, in terms of performance – including the software stack, a key element to take advantage of raw hardware power – SemiAnalysis sees AMD “rapidly improving.” SemiAnalysis also highlighted that OpenAI plans to support AMD’s GPUs, including MI300, in the standard Triton distribution starting with the upcoming 3.0 release. AMD joins the “AI PC” race Besides Intel, AMD is also touting the “AI PC” concept – that is, adding AI capabilities to mainstream x86 PC processors. The new AMD Ryzen 8040 Series mobile processors feature an integrated Ryzen AI NPU on-die on select models, offering up to 1.6x more AI processing performance than prior AMD models. AMD is also making Ryzen AI3 Software available for users to build and deploy machine learning models on their AI PCs. Laptops with Ryzen AI can offload AI models to the NPU, thereby freeing up the CPU to reduce power consumption while extending battery life. AMD Ryzen 8040 Series processors are expected to be available from OEMs including Acer, Asus, Dell, HP, Lenovo, and Razer, beginning in Q1 2024. Smartphone upturn; Synopsys revenues; Amkor in Arizona; smaller AC/DC adapters; 22.9 Pbits/s on a fiberDecember 4th, 2023 by Roberto Frazzoli

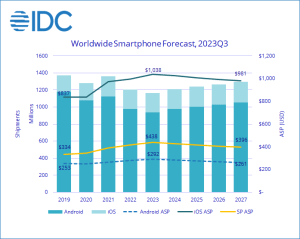

Let’s start this week’s news roundup with a “chip war” update which does not concern China. The Biden administration has reportedly forced a Saudi venture capital firm to sell its shares in Silicon Valley AI chip startup Rain Neuromorphics. According to Reuters, the move follows other actions the US has taken to slow AI development in the Middle East. Smartphone market is set for an upturn According to International Data Corporation (IDC), the drop in smartphone sales is finally over: the market research firm expects worldwide smartphone shipments to grow 7.3% year-over-year in the fourth quarter of 2023. The market recovery will continue in 2024 with 3.8% growth expected, followed by low single-digit growth for the rest of the forecast period, resulting in a five-year compound annual growth rate of 1.4%. According to IDC, the smartphone sector is entering the new era of low single-digit growth and lengthened refresh cycles, as the market is maturing. While the total available market will remain below pre-pandemic shipment levels throughout the forecast, average selling prices and market value will remain significantly higher than before. Synopsys 2023 revenues Synopsys has reported results for its fourth quarter and fiscal year 2023. Revenue for the fourth quarter of fiscal year 2023 was $1.599 billion, compared to $1.284 billion for the fourth quarter of fiscal year 2022. Revenue for fiscal year 2023 was $5.843 billion, an increase of approximately 15% from $5.082 billion in fiscal year 2022. A quick look at some IEDM innovations; bioinspired neural networks; EDA updatesNovember 27th, 2023 by Roberto Frazzoli

Will artificial intelligence ever be able to replicate biological brains? It’s a fact that research is advancing on all fronts. On the one hand, the semiconductor industry continues to push transistor size reduction – examples can also be found in some of this year’s IEDM papers – paving the way to systems comprising an ever larger number of transistors. On the other hand, scientists have started bridging artificial intelligence and neurosciences to explore overall network structures – as in recent research from Cambridge University – extending the concept of “neuromorphic” beyond using spiking neurons. This week we will briefly touch these topics – but first, a couple of EDA-related updates. Cloud-based simulation of mechanical stress for TSMC’s 3D packaging Ansys has collaborated with TSMC and Microsoft to validate a joint solution for analyzing mechanical stresses in multi-die 3D-IC systems manufactured with TSMC’s 3DFabric advanced packaging technologies. The solution is based on Ansys Mechanical finite element analysis software running on Microsoft Azure cloud infrastructure. 3D-IC systems often have large temperature gradients that lead to intense mechanical stresses between components due to differential thermal expansion. These stresses can lead to cracking or shearing of the connections between various elements. Simulating thermomechanical stress for large and complex devices, while maintaining predictive accuracy, requires substantial computing power. New release of QuickLogic tool suite QuickLogic has released version 2.4 of its Aurora eFPGA development tool suite. According to the company, this newest version integrates core tool enhancements that improve the eFPGA utilization and performance of designer’s RTL, particularly in the area of reconfigurable computing. The tool suite integrates fully open-source modules for scalability, longevity, and full code transparency. New features include asymmetric BlockRAM (BRAM) inferencing to reduce the need for manual modification of a user’s RTL design; single stage routing algorithm that boosts maximum operating frequency of a design by up to 24%; power calculation; and other new functionalities. Read the rest of A quick look at some IEDM innovations; bioinspired neural networks; EDA updates Synopsys.ai Copilot; Autodesk-Allegro integration; Microsoft’s chips; circumvention of export restrictionsNovember 20th, 2023 by Roberto Frazzoli

According to the latest forecast from International Data Corporation (IDC), the semiconductor market has reached a bottom and will soon return to growth. For 2023, the market research firm has revised its September forecast and now estimates that worldwide semiconductor revenue this year will grow to $526.5 billion – down 12% from $598 billion in 2022, but up from the previously estimated $519 billion. For 2024, IDC expects year-over-year growth of 20.2% to $633 billion, up from $626 billion in the prior forecast. Growth in 2024-2026 will be fueled by AI silicon, which by the end of this forecast period will account for almost $200 billion in semiconductor revenues. Synopsys.ai Copilot Synopsys has announced Synopsys.ai Copilot, the result of a collaboration with Microsoft to integrate Azure OpenAI Service that brings GenAI into the design process for semiconductors. According to the company, Synopsys.ai Copilot works alongside designers in the Synopsys tools they use every day, enabling conversational intelligence, in natural language, across the design team. Deployable in any on-prem or on-cloud environment, Synopsys.ai Copilot integrates Microsoft Azure on-demand computing infrastructure. Autodesk’s Fusion is now integrated with Cadence’s Allegro X and OrCAD X Autodesk’s Fusion mechanical CAD platform has been integrated with Cadence’s Allegro X and OrCAD X PCB design platforms. The collaboration between the two companies aims at solving the problems of current manual design data methods, which require electrical and mechanical engineers to exchange files that can differ from design intent – resulting in errors, unnecessary re-work and costly delays. According to the two companies, the integrated solution enables seamless bi-directional communication between PCB designers and mechanical engineers. Risc-V updates; chiplets in automotive applications; GenAI on smartphones; China’s advanced NAND chipNovember 13th, 2023 by Roberto Frazzoli

Japan’s government will reportedly allocate roughly $13 billion to boost its semiconductor industry. Part of this money is expected to be used to support TSMC and the recently founded Japanese foundry venture Rapidus. Let’s now move to the other news, which this week includes some announcements from Risc-V Summit North America. Risc-V updates Synopsys has extended its ARC Processor IP portfolio to include new Risc-V ARC-V Processor IP. The new Risc-V family includes the 32-bit ARC-V RMX embedded processor IP, scheduled to be available in Q2 of 2024; and the 32-bit ARC-V RHX real-time processor IP and 64-bit ARC-V RPX host processor IP, both scheduled to be available in the second half of 2024. Synopsys also announced it has joined the Risc-V International Board of Directors and Technical Steering Committee. Ventana has announced the second generation of its Veyron family of datacenter Risc-V processors. According to the company, the new Veyron V2 is the highest performance Risc-V processor available today. It is offered in the form of chiplets and IP. Besides datacenters, V2 targets automotive, 5G, AI, and client applications. Using AI against EM-IR violations; multi-vendor EDA tools on a single cloud; the 92-billion transistor Apple processorNovember 6th, 2023 by Roberto Frazzoli

Risc-V starts attracting attention in the context of U.S.-China “chip war”: a bipartisan group of eighteen U.S. lawmakers that includes five Democrats is reportedly asking the Biden administration to prevent China from achieving dominance in Risc-V technology at the expense of U.S. national and economic security. Let’s now move to this week’s news roundup, starting with some EDA updates. EDA updates: Cadence, Synopsys, Accellera The new Cadence Voltus InsightAI is – according to the company – the industry’s first generative AI technology that automatically identifies the root cause of EM-IR drop violations early in the design process and selects and implements the most efficient fixes to improve power, performance, and area (PPA). As Cadence maintains, users of Voltus InsightAI can fix up to 95% of violations prior to signoff, leading to a 2X productivity improvement in EM-IR closure. The new Synopsys Cloud OpenLink program enables chip designers to seamlessly access EDA tools and IP from multiple vendors in the Synopsys Cloud environment. As part of this initiative, the company is releasing an API specification that Synopsys Cloud OpenLink program members can use to deploy system-level integration with a secure and reliable transfer of entitlements to Synopsys Cloud. Accellera has announced the availability of the Clock Domain Crossing (CDC) Draft Standard 0.1 for public review. This standard aims to ease SOC integration, which often involves combining in-house and externally purchased IPs. The public review is open through December 31, 2023. |

|

|

|||||

|

|

|||||

|

|||||