The Breker Trekker Tom Anderson, VP of Marketing

Tom Anderson is vice president of Marketing for Breker Verification Systems. He previously served as Product Management Group Director for Advanced Verification Solutions at Cadence, Technical Marketing Director in the Verification Group at Synopsys and Vice President of Applications Engineering at … More » Catching Up with Portable StimulusApril 26th, 2016 by Tom Anderson, VP of Marketing

Ever since Accellera started the Portable Stimulus Working Group (PSWG), this emerging technology has generated a lot of buzz both within the EDA industry and among our semiconductor and systems customers. As the pioneer in this technology we get a lot of questions about what portable stimulus is, why it is different from the Universal Verification Methodology (UVM) and other established approaches, and why anyone would need it. We’ve devoted quite a few posts to this topic in The Brekker Treker blog, stretching back two years to when Accellera first set up a proposed working group (PWG) to survey the industry and decided whether standardization of portable stimulus was feasible and desirable. Given the many posts scattered throughout the past two years, we thought that we would take this opportunity to give readers new to this topic a guided tour of the information that we have available.

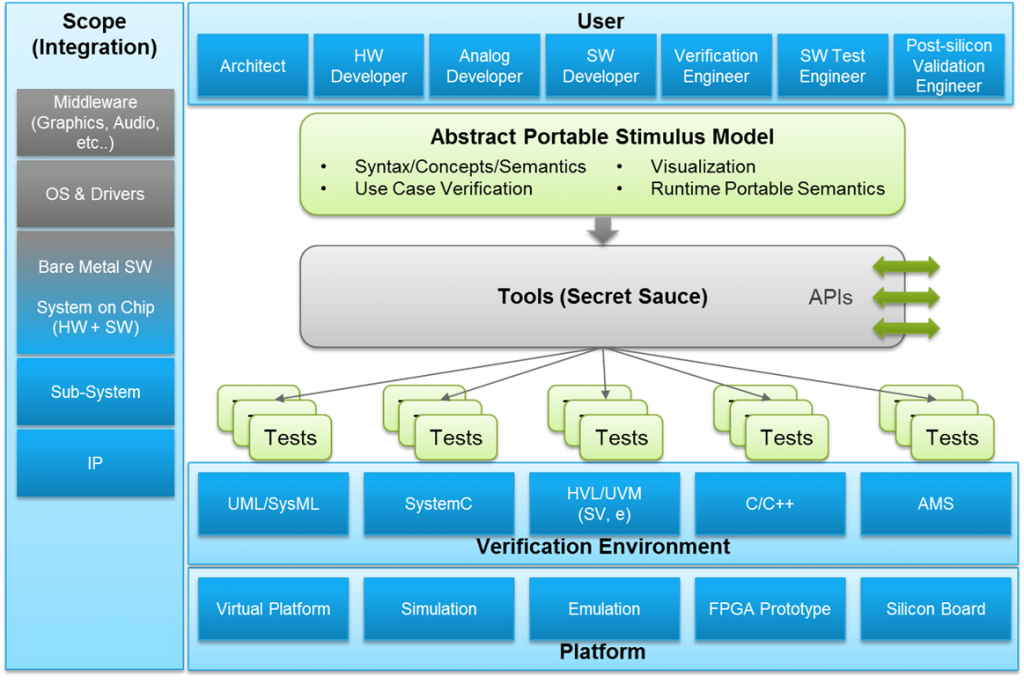

If you want to go back to the beginning, after the first meeting of the PWG was held we summarized the results and discussed the arguments for standardization: We pledged at that time to participate actively in the PWG, and indeed we did just that. As more people from more companies joined the group, we heard the first stirrings of what has become a loud buzz about this effort. We were pleasantly surprised by how much portable stimulus dominated conversations at DVCon India in 2014, where our CEO Adnan Hamid presented three talks: The PWG developed a list of more than 100 requirements for the portable stimulus space and generated some helpful documentation to define the scope that the proposed standard would cover. The most broadly distributed part of this material is a single diagram that captures the intent of the group’s work: Note that this diagram includes portability from IP to system level, from high-level simulation to hardware, and across multiple user communities. The PWG recommended that Accellera form a working group for a standard to meet the scope of this diagram, and the PSWG was officially announced in February of last year: Attendees at the Silicon Valley version of DVCon showed considerable interest in the new group and the concept of portable stimulus in general. We felt that there was some confusion in the industry because of the “portable stimulus” term. First of all, any verification tests must include results checking and coverage in addition to stimulus. Further, the tests themselves do not need to be portable. What must be portable is an abstract model, as shown in the Accellera diagram, from which tests appropriate for all verification levels and platforms can be generated: Right about this time last year, we wrote a series of blog posts looking at possible options for a format to describe the abstract portable stimulus model:

After looking at all the pros and cons, we concluded that C++ was the best choice for a portable stimulus standard because of both its wide usage and its powerful capabilities: In our previews and summaries of various conferences, we noted an ever-growing emphasis on portable stimulus. In particular, this year’s DVCon Silicon Valley included an Accellera PSWG update, a great presentation from our customer Cavium on verifying a multi-SoC project with 144 CPU cores, and a focus on portable stimulus by both Cadence and Mentor:

And so this takes us up to the present, where Breker and a broad mix of EDA and user companies continue to work diligently within PSWG on a standard. As we said a few weeks ago, you do not need to wait for a standard to start using portable stimulus. Please come join the ranks of Breker customers now, and we’ll migrate you to the standard when it’s available: We hope that this recap will serve as a handy introduction to portable stimulus, the PSWG, and Breker’s role both in creating a standard and in pioneering the market. If we missed anything or you have any questions, please comment. Tom A. The truth is out there … sometimes it’s in a blog. Tags: Accellera, Breker, bring-up lab, C/C++, cache coherency, Cadence, Cavium, constraints, dvcon, DVCon India, EDACafe, emulation, ESL, FPGA, functional verification, graph, graph-based, mentor, multi-SoC, portable stimulus, prototyping, PSWG, scenario model, simulation, SoC validation, SoC verification, system-on-chip, SystemVerilog, test case generator, test cases Warning: Undefined variable $user_ID in /www/www10/htdocs/blogs/wp-content/themes/ibs_default/comments.php on line 83 You must be logged in to post a comment. |

|

|

|||||

|

|

|||||

|

|||||