EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Synopsys tackles the ECO challenges with PrimeClosureNovember 1st, 2022 by Roberto Frazzoli

Thanks to real-time integration with the physical design flow and to new optimization algorithms, the solution promises dramatic TAT improvements and significant PPA benefits for large SoCs and multi-die designs – running on single box hardware Major EDA vendors are launching new products to address the challenges of design closure and ECOs in deep-submicron SoCs. On October 5th Synopsys introduced its new PrimeClosure solution. Jacob Avidan, senior vice president of Engineering for the Silicon Realization Group at Synopsys, described the features of PrimeClosure in the video interview he recently gave to EDACafe’s Sanjay Gangal. Building on that interview, in this article we will add some more details about the new solution by means of the answers that Manoj Chacko, Director of Product Marketing for Synopsys PrimeClosure, provided to our additional questions. Read the rest of Synopsys tackles the ECO challenges with PrimeClosure Cadence’s Certus, a new approach to speeding up full-chip optimization and signoffOctober 24th, 2022 by Roberto Frazzoli

Based on a parallel architecture and a ‘distributed optimization engine’, the new automated environment builds on Cadence’s implementation system (Innovus) and timing signoff solution (Tempus), and promises up to 10X faster closure for designs greater than ten million cells With SoCs targeted at advanced applications getting ever larger and complex, moving from block-level optimization to full-chip design closure has become a challenging and time-consuming task for design teams. The current, manual full-chip closure flow involves many steps and iterations – from assembly, static timing analysis, and optimization and signoff with hundreds of views. According to Cadence, today’s design teams often spend five to seven days per iteration to meet chip-level signoff timing and power requirements, therefore this error-prone process can take designers months to converge. Additionally, current methodologies are considered inefficient in terms of team collaboration and user experience. Addressing these problems, Cadence has recently launched Certus Closure Solution, an environment aimed at accelerating full-chip design closure by means of a parallel architecture and automation of previously manual tasks. Brandon Bautz – Senior Group Director of Product Management, responsible for the Cadence silicon signoff and verification product lines in the Digital & Signoff Group at Cadence – described the features of Certus in the video interview he recently gave to EDACafe’s Sanjay Gangal. In this article we will add some more details about Certus, building on that video interview and on the answers Bautz provided to our additional questions. Read the rest of Cadence’s Certus, a new approach to speeding up full-chip optimization and signoff New export controls; EDA updates; AI training on small memory devices; cable cooling for 1,400 A battery chargingOctober 14th, 2022 by Roberto Frazzoli

New export controls have been in the spotlight over the past few days. Other news this week include several EDA updates and some interesting academic research. New U.S. controls on export to China The U.S. Government is implementing new export controls on advanced computing and semiconductor manufacturing items to the People’s Republic of China. Details of the new rules can be found here and here. According to Bloomberg, these additional restrictions will not apply to the China-based fabs owned by South Korean chipmakers SK Hynix and Samsung. In fact, SK Hynix Inc has reportedly said it has received authorization from the U.S. Department of Commerce to receive chip equipment needed for its chip production facilities in China for one year, without seeking additional licensing requirements. Cadence Certus aims to accelerate design closure Cadence has announced the new Certus Closure Solution environment, to automate and accelerate the complete design closure cycle – from signoff optimization through routing, static timing analysis and extraction. Key to acceleration is a massively parallel and distributed architecture enabling concurrent processing. According to Cadence, the solution supports the largest chip design projects with unlimited capacity while improving productivity by up to 10X versus current methodologies and flows. EDA updates on ECO, DFT; Samsung’s roadmap; Intel Innovation; new fabs; EU common chargerOctober 7th, 2022 by Roberto Frazzoli

Plenty of news from the whole ICT-semiconductor ecosystem this week, some of them with a common underlying theme: the advent of chiplet-based 3D devices. Let’s start with some EDA updates. Synopsys’ ‘streaming fabric’ for silicon lifecycle management Synopsys has announced a streaming fabric technology aimed to shorten both silicon data access and test time – by up to 80%, according to the company – while also minimizing excessive power. Generated by Synopsys TestMAX DFT tool and part of Synopsys’ silicon lifecycle management flow, the new streaming fabric is an on-chip network that transports silicon data to and from multiple design blocks and multi-die systems. According to Synopsys, the fabric calls for minimal planning effort and has a limited physical impact on design. Additionally, a new power estimation technology incorporated in Synopsys TestMAX ATPG solution more accurately determines power drawn at data application time. Synopsys’ new ECO solution Synopsys has also announced PrimeClosure, a golden signoff ECO (engineering change order) solution that addresses lengthy engineering design closure times. According to the company, early customers have achieved up to 45% better timing, up to 10% better power, up to 50% fewer ECO iterations and up to 10x higher design productivity compared to traditional ECO flows. PrimeClosure has direct access to incrementally enabled placement, routing, extraction, physical verification, equivalence checking and signoff technologies from the other Synopsys tools, and is integrated with Ansys RedHawk-SC digital power integrity signoff solution, enabling to account for and fix up to 50% of late-stage dynamic voltage drop violations and maximize energy efficiency without impacting chip timing. Cadence tackles verification productivity with AI-based VerisiumSeptember 30th, 2022 by Roberto Frazzoli

A closer look at the new platform – currently focused on debugging – with the help of Cadence’s Matt Graham With ever-growing device size and complexity, SoC verification has become an extremely challenging task, often requiring more compute time and qualified human resources than any other step in the engineering flow. According to a Cadence estimate, the verification effort can often climb to more than 500 years of compute time – with tens of millions of runs and hundreds of millions of coverage bins, to uncover thousands of bugs. Debugging alone can consume multiple weeks of time of many engineers. In terms of time-to-market, therefore, verification can be considered a key limiting factor and a potential cause of schedule slips. Reconciling a thorough verification coverage with a tight SoC development schedule clearly calls for better productivity through automation, an even more challenging goal. A new approach to improving verification productivity is now proposed by Cadence with its Verisium Artificial Intelligence-Driven Verification Platform – a suite of applications leveraging big data and AI to optimize verification workloads, boost coverage and accelerate root cause analysis of bugs. The Verisium platform is built on the new Cadence Joint Enterprise Data and AI (JedAI) Platform and is natively integrated with the Cadence verification engines. The initial suite of apps available in the Verisium platform is focused on debugging, a very significant part of verification. Matt Graham, group director at Cadence Design Systems, described the Verisium apps in the video interview he recently gave to EDACafe’s Sanjay Gangal; in this article we will summarize his answers and add a few details, as well as the responses he provided to some additional questions.

Read the rest of Cadence tackles verification productivity with AI-based Verisium CHIPS Act updates; single-SoC automotive architecture; neural rendering; 2022 IEEE roadmapSeptember 23rd, 2022 by Roberto Frazzoli

New developments have emerged on the implementation of the U.S ‘CHIPS and Science Act’. More news this week include both Nvidia and Qualcomm advocating the unification of automotive electronic functions in a single system-on-chip. But first, an EDA update. Synopsys’ unified emulation and prototyping system Synopsys has announced what it claims is “the industry’s first” unified hardware system for emulation and prototyping, based on its ZeBu EP1 emulation system. Unification enables a single verification hardware system to be used throughout the entire chip development lifecycle. According to Synopsys, users of the ZeBu EP1 system have achieved 19 MHz emulation and 100 MHz prototyping clock performance, enabling them to run large amounts of software pre-silicon and accelerate project schedules. The unified hardware system allows users’ verification and software development requirements to drive how and when to shift capacity between emulation and prototyping, rather than having to estimate early on how much of each resource might be needed. U.S. CHIPS Act updates: leadership team, innovation coalition The U.S. government has announced the leadership team which will be responsible for the implementation of the CHIPS and Science Act. Members of the team are Ronnie Chatterji, Michael Schmidt, Eric Lin, Todd Fisher, Donna Dubinsky, and J.D. Grom. Individual roles and bios are detailed in this press release. More than 100 businesses, startups, universities and nonprofits have formed the American Semiconductor Innovation Coalition (ASIC) with the specific goal of being selected by the Department of Commerce as the partner of choice for the newly created ‘National Semiconductor Technology Center’ and ‘National Advanced Packaging Manufacturing Program’ – both funded through the recently passed ‘CHIPS and Science Act’. Among others, ASIC members include AMD, Analog Devices, Ansys, Applied Materials, Cadence, DuPont, GlobalFoundries, IBM, KLA, Microsoft, Micron, MIT, Nvidia, Samsung, Siemens EDA, Synopsys, Texas Instruments. Some of the coalition members are headquartered in Europe, such as ASML, CEA-Leti, Fraunhofer, imec and Yole Développement. In terms of academic institutions, the ASIC member list currently published on the coalition website does not include neither Stanford University nor UC Berkeley. ASIC claims the ability to stand up an NSTC innovation hub in as little as six months. Among its key capabilities, the coalition mentions the already existing Albany NanoTech Complex. Cadence Verisium; Arm Neoverse V2; chipmaking in India; PyTorch Foundation; microwave annealing; 600 miles batteriesSeptember 16th, 2022 by Roberto Frazzoli

According to a Reuters report, the Biden administration plans next month to broaden curbs on U.S. shipments to China of AI chips and semiconductor equipment. The new regulations would be based on restrictions communicated in letters earlier this year to KLA, Lam Research and Applied Materials. The letters forbade these companies from exporting chipmaking equipment to Chinese factories that produce chips with sub-14 nanometer processes unless the sellers obtain Commerce Department licenses. Some of the sources quoted by Reuters said the regulations would likely include additional actions against China. Cadence new verification platform The new Cadence Verisium AI-Driven Verification Platform is a suite of applications leveraging big data and AI to optimize verification workloads, boost coverage and accelerate root cause analysis of bugs. Verisium is built on the new Cadence Joint Enterprise Data and AI (JedAI) Platform and is natively integrated with the Cadence verification engines. The initial suite in the Verisium platform includes multiple apps using machine learning to automate tasks such as regression failure triage; pinpoint potential bug hotspots caused by source code revisions; analyze waveforms looking for the root cause of a test failure; predict which source code check-ins are most likely to have introduced failures. More Verisium apps offer a debug solution from IP to SoC and from single-run to multi-run; and full flow IP and SoC-level verification management. CHIPS Act details; Arm suing Qualcomm; Risc-V updates; fast-charging batteries; GaN JBS diodesSeptember 9th, 2022 by Roberto Frazzoli

Major news updates this week include the first insights into how US taxpayers’ money will be used to support the domestic semiconductor industry. Among the other updates, fast-charging car batteries getting closer to mass production. Details of U.S. CHIPS Act implementation The U.S. Department of Commerce has released its implementation strategy for the $50 billion CHIPS Act. The program, called ‘CHIPS for America’, will be housed within the National Institute of Standards and Technology (NIST). Approximately three quarters of the incentives funding, around $28 billion, will be targeted to establish domestic production of leading-edge logic and memory chips that require the most sophisticated manufacturing processes available today. Arguably, Intel and Micron will be the main beneficiaries of this share. At least a quarter of the available CHIPS incentives funding, or approximately $10 billion, will be devoted to new manufacturing capacity for mature and current-generation chips, new and specialty technologies, and for semiconductor industry suppliers. The remaining $11 billion will be invested in new R&D initiatives – a National Semiconductor Technology Center, a National Advanced Packaging Manufacturing Program, up to three new Manufacturing USA Institutes – and in NIST metrology R&D programs. Some details about the conditions under which applicant companies will be granted ‘CHIPS for America’ funding have been provided by US Commerce Secretary Gina Raimondo during a press briefing at the White House. “This is not a blank check for companies,” she said. “This is not for them to pad their bottom line.” (…) “CHIPS funds cannot be used for stock buybacks. CHIPS funds are not intended to replace private capital,” she added. Raimondo then addressed issues specifically concerning China, explaining that beneficiary companies “are not allowed to use this money to invest in China, they can’t develop leading-edge technologies in China, they can’t send latest technology overseas.” (…) “Companies who receive CHIP funds can’t build leading-edge or advanced technology facilities in China for a period of 10 years. Companies who receive the money can only expand their mature node factories in China to serve the Chinese market,” she said. Export of some Nvidia and AMD products to China halted; Intel’s Risc-V IDE; AI chip reaches 30 TFlops/WSeptember 2nd, 2022 by Roberto Frazzoli

More U.S. and western European tech companies have reportedly closed their Russian operations: among them Dell, Logitech, Ericsson and Nokia. Another significant update on geopolitical matters is the export ban on some Nvidia and AMD products (see below). However, the effectiveness of sanctions against China is a debated issue – see, for example, this EETimes article – and reverse engineering on a SMIC chip has provided additional surprises: TechInsights has found many similarities in process technologies, designs and innovations between SMIC’s 7-nanometer and TSMC’s 7-nanometer nodes. According to TechInsights, also, it is a notable achievement for SMIC having moved from 14-nanometer to 7-nanometer in just two years, without access to the most advanced western equipment and technologies. Export restrictions on some advanced Nvidia GPUs and AMD accelerators Nvidia and AMD have reportedly been told by the US government to halt exports of certain high-performance chips and systems to China. As for Nvidia, the restrictions cover A100 and forthcoming H100 GPUs, and any systems that include them, effective immediately. AMD has reportedly been given new requirements by the US Department of Commerce that will hit shipments of its MI250 accelerator to China. In a regulatory filing, Nvidia said that the export restrictions are due to a potential risk of the products being used by, or diverted to, a “military end user.” Both companies said the new mandate also covers a ban in export to Russia. EDA in geopolitical tensions; new fabs and plants; processor market updatesAugust 26th, 2022 by Roberto Frazzoli

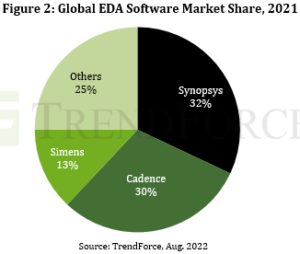

Catching up on some of the latest news after a summer break, two significant updates concern EDA as the subject of geopolitical tensions between China and the Western countries. More news in this week’s article includes new fab and packaging plant announcements – some of which spurred by the recently passed U.S. ‘CHIPS and Science Act’ – as well as updates concerning the processor market. U.S. export controls on EDA tools for GAA transistor design On August 12 the U.S. Commerce Department’s Bureau of Industry and Security issued a rule that establishes new export controls on four “emerging and foundational technologies” that are considered essential to the national security of the United States. Among them, two substrates of ultra-wide bandgap semiconductors – gallium oxide (Ga2O3) and diamond – and electronic CAD software specially designed for the development of integrated circuits with Gate-All Around Field-Effect Transistor structure. Ban on GAA design tools a potential problem for China, says TrendForce According to market research firm TrendForce, this new U.S. EDA software ban may actually affect China’s advanced IC design. The analysts observe that the three major U.S. EDA players (Synopsys, Cadence, and Siemens) account for a total 75% market share, and that Empyrean Technology – the leader of China’s EDA industry – has not yet touched upon GAA research and development. TrendForce also notes that even if China purchased a large amount of authorized EDA software before the current sanction takes effect, the United States could block its use by remotely denying license updates. In conclusion, according to TrendForce, without U.S. EDA tools, Chinese IC design – as well as Chinese foundries – will experience difficulties developing advanced 3-nanometer process design. Read the rest of EDA in geopolitical tensions; new fabs and plants; processor market updates |

|

|

|||||

|

|

|||||

|

|||||