EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Risc-V updates; chiplets in automotive applications; GenAI on smartphones; China’s advanced NAND chipNovember 13th, 2023 by Roberto Frazzoli

Japan’s government will reportedly allocate roughly $13 billion to boost its semiconductor industry. Part of this money is expected to be used to support TSMC and the recently founded Japanese foundry venture Rapidus. Let’s now move to the other news, which this week includes some announcements from Risc-V Summit North America. Risc-V updates Synopsys has extended its ARC Processor IP portfolio to include new Risc-V ARC-V Processor IP. The new Risc-V family includes the 32-bit ARC-V RMX embedded processor IP, scheduled to be available in Q2 of 2024; and the 32-bit ARC-V RHX real-time processor IP and 64-bit ARC-V RPX host processor IP, both scheduled to be available in the second half of 2024. Synopsys also announced it has joined the Risc-V International Board of Directors and Technical Steering Committee. Ventana has announced the second generation of its Veyron family of datacenter Risc-V processors. According to the company, the new Veyron V2 is the highest performance Risc-V processor available today. It is offered in the form of chiplets and IP. Besides datacenters, V2 targets automotive, 5G, AI, and client applications.

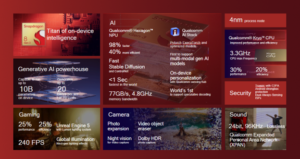

Andes and Vector are collaborating to develop integrated automotive solutions combining AndesCore Safety-Enhanced Risc-V processor series and Vector’s “Microsar” AUTOSAR software. Tasking’s system-level verification and debugging tools now support the Andes Risc-V ISO 26262 certified processor IPs and associated MachineWare virtual models. This collaboration equips SoC design teams with automotive-grade Risc-V IPs and the tools for early firmware and MCAL (Microcontroller Abstraction Layer) development. The OpenHW Group has announced the multi-member CORE-V CVA6 platform, an open-source FPGA-based software development and testing environment for Risc-V processors designed to provide a vendor-neutral environment for Risc-V software CI and testing that keeps pace with Risc-V standards. On occasion of Risc-V Summit North America, Risc-V International celebrated the impressive momentum across the Risc-V ecosystem in 2023. Today, Risc-V has more than 4,000 members representing 70 countries, with more than 75 technical working groups. In 2023, Risc-V has ratified 12 specifications. Some of the recent updates include the ratification of Vector Crypto ISA Package and the Input-Output Memory Management Unit (IOMMU) specification. Renesas’ automotive roadmap Renesas has recently unveiled its roadmap for its automotive SoCs and MCUs, providing advance information about the fifth generation R-Car SoC platform and two new Arm-based MCU platforms for vehicle control applications. Until the fourth generation, the R-Car SoCs were designed for specific use cases, such as ADAS/Autonomous Driving that requires high AI performance, and gateway solutions with enhanced communication capabilities. Renesas’ fifth-generation R-Car SoC will incorporate chiplet technology to create a flexible platform that can be customized to meet various requirements for each use case. As for vehicle control, Renesas is developing an Arm-based 32-bit crossover R-Car MCU platform with built-in Non-Volatile Memory that can deliver higher performance than traditional MCUs currently offer. Renesas is also extending its vehicle control portfolio with a new R-Car MCU series, which will be also powered by Arm. The importance of chiplets for the future of automotive applications has also been stressed by Belgian research institute imec, which has recently held its second Automotive Chiplet Conference. The fifty participating companies created two working groups focusing on architecture and standardization, respectively. Generative AI on smartphones: Qualcomm, MediaTek Both Qualcomm and MediaTek have recently introduced their latest flagship smartphone chips, and both boast on-device Generative AI capabilities – besides a ton of other features. Qualcomm’s Snapdragon 8 Gen 3 Mobile Platform includes an AI engine which – according to the company – is the world’s first to support generative AI models with up to 10 billion parameters on-device. The new chip also integrates Qualcomm Hexagon NPU, Kryo CPU, and Adreno GPU, promising substantial performance improvements. MediaTek’s Dimensity 9300, the company’s newest flagship mobile chip, promises unmatched user experiences in gaming, video capture, and on-device generative AI processing. The chip is built on TSMC’s third generation 4nm process, with four Arm Cortex-X4 cores operating up to 3.25GHz and four Cortex-A720 cores operating up to 2.0GHz. It also includes MediaTek’s APU 790 AI processor supporting large language models with 1B, 7B, and 13B parameters. With its Arm Immortalis-G720 GPU, the Dimensity 9300 offers an almost 46% boost in GPU performance compared to the previous Dimensity 9200, with the same power consumption. China’s YMTC fabricates the world’s most advanced 3D NAND memory chip According to Canadian reverse engineering firm TechInsights, China’s YMTC has succeeded in fabricating the world’s most advanced 3D NAND memory chip. “This is the first quad-level cell (QLC) 3D NAND die with more than two hundred active word lines that TechInsights has seen,” the firm stated, adding that the die has the highest bit density seen in a commercially available NAND product at 19.8 Gb/mm2. The 232-layer QLC 3D NAND die was found in the ZhiTai Ti600 1TB solid state drive. “Evidence is mounting that China’s momentum to overcome trade restrictions and build its own domestic semiconductor supply chain is more successful than expected,” TechInsights commented. Acquisitions Keysight, which currently owns 50.6% of the share capital of French company ESI Group, has announced the filing of the tender offer for all remaining outstanding shares. ESI Group provides virtual prototyping software. Vishay will acquire Nexperia’s wafer fabrication facility and operations located in Newport, South Wales, UK – an automotive certified, 200mm semiconductor wafer fab that supplies primarily automotive markets. It is the largest semiconductor manufacturing site in the UK. Vishay will use the fab to produce its SiC Trench MOSFETs and diodes. Further reading “Semiconductor Crisis and Roadmaps Rescues” is the headline of a 54-page editorial recently authored by Paolo Gargini, Intel veteran and Chairman of IRDS (IEEE’s International Roadmap for Devices and Systems). The paper reviews four semiconductor crisis, from the first one in 1957 to the most recent one in 2020, while recalling the evolution of technologies and markets. Among many other interesting concepts, Gargini tracks the origin of Silicon Valley back to the foundation of DARPA in 1957 as a reaction to the launch of Russian satellite Sputnik. Buying transistors, the US Government “became the number 1 venture capitalist in semiconductors and created Silicon Valley,” according to Gargini. |

|

|

|||||

|

|

|||||

|

|||||