The Breker Trekker Tom Anderson, VP of Marketing

Tom Anderson is vice president of Marketing for Breker Verification Systems. He previously served as Product Management Group Director for Advanced Verification Solutions at Cadence, Technical Marketing Director in the Verification Group at Synopsys and Vice President of Applications Engineering at … More » A Snapshot Update on the Accellera Portable Stimulus EffortMarch 16th, 2016 by Tom Anderson, VP of Marketing

As all of our regular readers are aware, the software-driven SoC verification space pioneered by Breker is becoming more of a mainstream approach every day. One good barometer for the industry shift now underway is the standardization effort in progress within the Accellera Portable Stimulus Working Group (PSWG). The amount of interest in this standard has skyrocketed recently, and portable stimulus was a hot topic at the Design and Verification Conference and Exhibition (DVCon) two weeks ago. As we promised when we first began discussing the PSWG, we don’t believe in sharing internal details of standardization work in a public blog. However, the group was offered a slot to present an update at an Accellera-sponsored lunch during DVCon. So the PSWG put together a set of slides with information to share publicly and Vice-Chair Tom Fitzpatrick of Mentor did a nice job of presenting them. For those of you who could not attend, we’ll summarize the current status in today’s blog post.

The update began by noting that the PSWG was officially formed in late 2014 following a Proposed Working Group (PWG) that assessed whether portable stimulus was an appropriate topic for standardization. The PWG reviewed a number of position statements from both EDA vendors and user companies, and then merged their needs into an extensive list of 117 requirements for a portable stimulus solution. These requirements were ranked in priority order. The group defined three main goals for the standard:

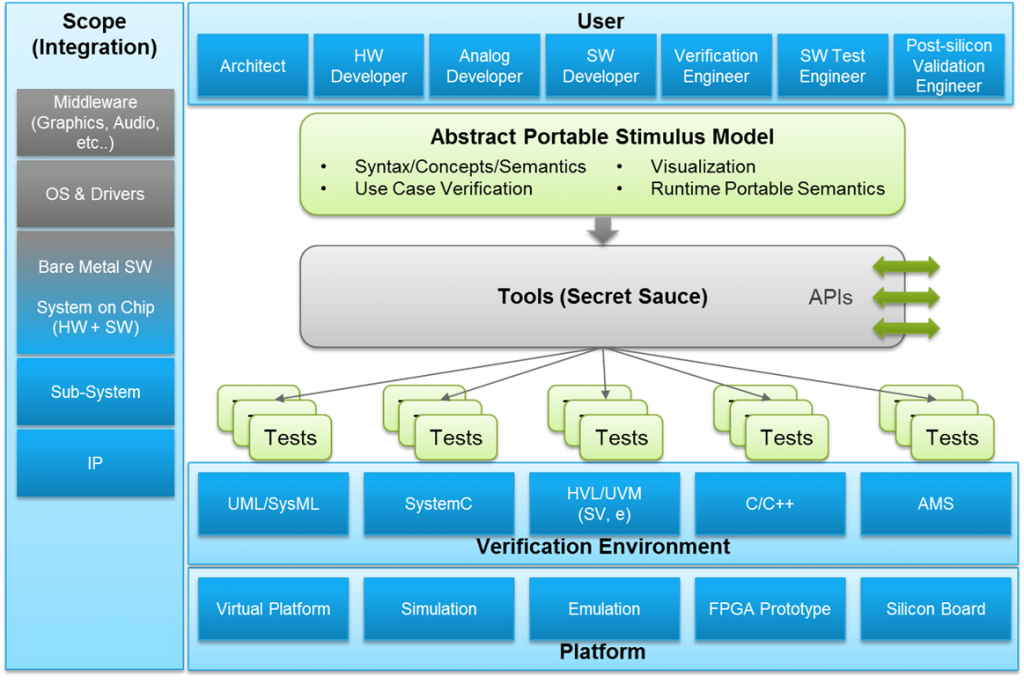

The PWG also developed a single diagram that does a remarkably good job of capturing the goals, requirements, and intended scope of the standard: To ensure that the standard would solve real-world verification problems, the PSWG members defined a set of concrete use-case examples, currently numbering 17, that will be used to scope the requirements and assess the contributions proposed as the basis for the standard. These examples span portable verification of such use cases as memory-to-memory system data paths, DMA allocation for peripherals, exhaustive exercise of power states, and pad selection connectivity. With this as background, the PSWG solicited proposals to serve as the baseline for a standard. Three such contributions have been made to Accellera. Breker proposed a solution based on C/C++ with a class library and an API. The combination of these features brings more declarative specification, value constraints, and (graph) path constraints into C++. Note, however, that the syntax of our proposal lies entirely within C++11, with no extensions or non-standard constructs. Cadence and Mentor are championing a proposal for a new domain-specific language for portable stimulus specification. It supports graph-based specification of scenario and coverage in the new language while providing links to existing C/C++ or SystemVerilog code. The proposal does not allow scenario specification directly in C++; the constructs of the new language must be used. Finally, Vayavya has proposed a hardware-software interface (HSI) using C++ that could layer on top of either of the other two proposals. That quick summary brings you fully up to speed on where the PSWG sits today. All four proposing companies are responding to comments and suggestions from other members with a goal to update and finalize their specifications before the end of March. Ultimately the group will have to select the Breker proposal, the Cadence-Mentor proposal, or some sort of hybrid proposal as the baseline for the standard. At that point all the other details of completing and documenting the standard can proceed, targeting a full version 1.0 release in January, 2017. We’d like to know what you think. We know that the majority of likely users of this standard are already C/C++ programmers. Leveraging C++ means no new language to learn and a minimal ecosystem for vendors to develop. We believe that developing a new language is a major effort that should only be undertaken if no existing language can do the job. We’ve shown that C++ is up to the task. On the other hand, supporters of the new language argue that its domain-specific limitations will make it easier to learn and use. If you have thoughts either way, we would love to have your comments. We also encourage you to get involved in the PSWG to share your expertise. The group has only eight user companies (AMD, Analog Devices, Cisco, IBM, Intel, NVIDIA, NXP, and Qualcomm) active at this point. That’s a great list, but even more user input is better. Of course we welcome any questions at all on portable stimulus or PSWG, and any level of involvement that you can manage. We hope to be hearing from you! Tom A. The truth is out there … sometimes it’s in a blog. Tags: Accellera, Breker, bring-up lab, C/C++, cache coherency, Cadence, constraints, dvcon, emulation, ESL, FPGA, functional verification, graph, graph-based, mentor, multi-SoC, node coverage, portable stimulus, prototyping, PSWG, realistic use case, scenario model, simulation, SoC validation, SoC verification, system-on-chip, SystemVerilog, test case generator, test cases, use-case coverage, vayavya Warning: Undefined variable $user_ID in /www/www10/htdocs/blogs/wp-content/themes/ibs_default/comments.php on line 83 You must be logged in to post a comment. |

|

|

|||||

|

|

|||||

|

|||||