The Breker Trekker Tom Anderson, VP of Marketing

Tom Anderson is vice president of Marketing for Breker Verification Systems. He previously served as Product Management Group Director for Advanced Verification Solutions at Cadence, Technical Marketing Director in the Verification Group at Synopsys and Vice President of Applications Engineering at … More » If Your Chip Is Not a Cache-Coherent SoC, It Soon Will BeNovember 25th, 2014 by Tom Anderson, VP of Marketing

Yes, we know that the title of this week’s post sounds a lot like two previous posts. We wanted to link together the two threads from those posts into a single message that we believe reflects what is happening right now in the world of complex chips. This is a short summary in line with the short week due to the Thanksgiving holiday here in the United States. The line of argument is straightforward:

While most of these statements are not universally true, they reflect a significant sea change that we see every day when discussing current and future projects with our customers.

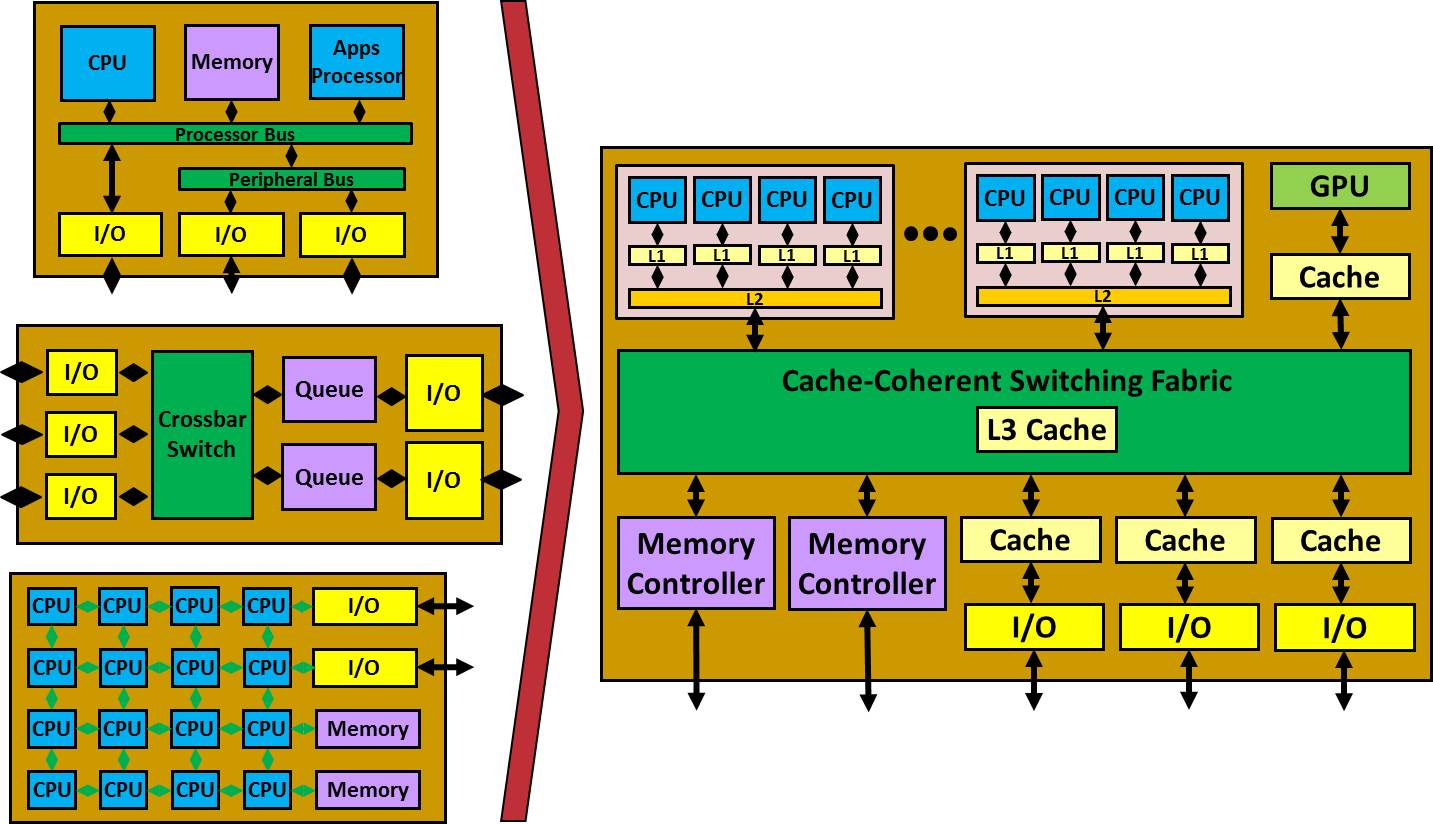

In some ways, most large chips are starting to look like the SoCs for smartphone and tablets that we targeted when we introduced TrekSoC three years ago. We’ve added the following diagram to many of our presentations, and have received general acceptance from engineers in various industries. This diagram succinctly captures our observation that simple bus-based SoCs, non-SoCs such as networking chips, and arrays of processors are all moving toward multi-processor, shared-memory, multi-level-cache-coherent SoCs. It is precisely this industry transition that is driving intense interest in TrekSoC, TrekSoC-Si, and our Coherency TrekApp. As this transition happens, cache coherency moves from the domain of the CPU architect to become a problem for everyone designing and verifying SoCs. We’ve made some fairly bold claims here, but they do reflect what are seeing and hearing. If your world is changing in this way, then we have the solutions for cache coherency pre-silicon verification and post-silicon validation available today. If your view of the chip and SoC industry does not match ours, please submit a comment so that we can get a lively debate going. Thanks, and if you have time off this week please enjoy it. Tom A. The truth is out there … sometimes it’s in a blog. Tags: Breker, cache, Carbon, coherency, CPAK, DV, functional verification, IoT, IP, portable stimulus, SoC, SoC verification, TrekApp, TrekSoC, TrekSoC-Si, uvm, VIP Warning: Undefined variable $user_ID in /www/www10/htdocs/blogs/wp-content/themes/ibs_default/comments.php on line 83 You must be logged in to post a comment. |

|

|

|||||

|

|

|||||

|

|||||