EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Wafer-on-Wafer; ExaFlops supercomputers; Arm management change; Canadian battery plantsMarch 10th, 2022 by Roberto Frazzoli

IDC is among the first market research firms trying to provide an initial assessment of how the Ukraine war will affect ICT spending and technology markets worldwide. Consequences are expected on many aspects of the business environment – and will arguably affect the semiconductor ecosystem, too. Hoping for peace, let’s now move to some tech news. Incubators updates: Analog Devices (Ireland), Infineon (Hong Kong) Analog Devices will invest €100 million over the next three years in ADI Catalyst, a 100,000 square foot custom-built facility for innovation and collaboration located at its campus in the Raheen Business Park in Limerick, Ireland. This latest phase of expansion will also see the creation of 250 new jobs in the Irish market by 2025. The Catalyst project is supported by the Irish Government through IDA Ireland. Hong Kong Science and Technology Parks Corporation (HKSTP) has partnered with Infineon Hong Kong in a three-year co-incubation program targeted at microelectronics startups. Advanced packaging and 3D updates: Apple’s Ultrafusion, Graphcore’s Wafer-on-Wafer Apple has recently announced M1 Ultra, its new Arm-based SoC that will power the next Mac personal computers. The device uses Apple’s UltraFusion packaging architecture to interconnect the die of two M1 Max chips through a silicon interposer conveying more than 10,000 signals, providing 2.5TB/s of low latency bandwidth. This enables M1 Ultra to behave and be recognized by software as one chip, so developers don’t need to rewrite code. The new SoC consists of 114 billion transistors and features a 20-core CPU, a 64-core GPU, and a 32-core neural engine. Graphcore has recently unveiled what it claims is the world’s first 3D Wafer-on-Wafer processor – the Bow IPU – built using TSMC’s Wafer-on-Wafer 3D technology. In the new device, two wafers are bonded together to generate a new 3D die: one wafer for AI processing, which is architecturally compatible with the preexisting Graphcore GC200 IPU processor, and a second wafer for power delivery die. By adding deep trench capacitors in the latter die, right next to the processing cores and memory, Graphcore claims to be able to deliver power much more efficiently – enabling a 40% increase in performance. More details have been disclosed in this EETimes article. As the company explained, the two wafers are bonded – metal sides together – without any interstitial bumps, in a sort of cold weld, achieving an extremely high density of interconnect. The device also uses ‘back-side through-silicon vias’ (BTSVs) which allow connection to layers inside the wafer sandwich. Graphcore points out that Wafer-on-Wafer is different from chip-on-wafer technologies, and that aligning two entire wafers is easier rather than two die. This – along with the use of an ion etch process for BTSVs – results in a finer connection pitch. Graphcore has also announced it will use the next generation of its IPU technology to build an AI supercomputer that will reach over 10 ExaFlops of AI floating point compute. The system – called ‘the Good Computer’ in honor of computer science pioneer Jack Good – is expected to be available by 2024. Intel’s German fab; chiplet interconnect standard; Qualcomm’s 3nm foundry order; Altair acquires Powersim; impact of Ukraine warMarch 3rd, 2022 by Roberto Frazzoli

The unrelated themes of war in Ukraine and semiconductor investments crossed each other on TV screens last Tuesday when Intel’s CEO Pat Gelsinger appeared with a Ukrainian flag on his jacket during the State of the Union Address. Gelsinger, whom President Joe Biden gave a shoutout praising Intel’s plan for a mega-fab in Ohio, attended the speech as a guest in the First Lady’s viewing box. Ukraine war is also a topic of our news roundup this week, as we try to monitor its impact on the semiconductor ecosystem and on IT in general. But first, some industry updates. EDA updates: Breker, Mirabilis, open source FPGA tools Breker Verification Systems has unveiled SystemUVM, a framework designed to simplify specification model composition for test content synthesis with a UVM/SystemVerilog syntactic and semantic approach familiar to universal verification methodology (UVM) engineers. According to Breker, by leveraging synthesis for test content generation, a 5X improvement for larger components and multi-IP subsystems is common in composition time combined with significant coverage increases. Mirabilis Design has released its new VisualSim MicroArchitecture Modeler, what it claims is the first solution to enable verification of the micro-architecture of the entire SoC at cycle-per-cycle. According to Mirabilis, processor core vendors do not provide cycle-accurate models for high-end cores. Instead of resorting to expensive emulators or extremely slow RTL execution, VisualSim MicroArchitecture Modeler runs 10000+ instructions per second and still maintain a 85-95% accuracy. The solution employs a library of customizable IP components. Cadence’s 2021 results; Intel Investor Meeting; China’s wafer capacityFebruary 24th, 2022 by Roberto Frazzoli

War in Europe is obviously our top news update this week, even though war coverage is the job of TVs and daily newspapers. For our part, going forward we will try to monitor the impact that this tragic event is going to have on the semiconductor ecosystem and on the IT industry – in terms of supply chain disruptions, sanctions consequences and so on. For the moment, let’s move to our usual weekly news update. Cadence’s 2021 results Cadence achieved a revenue growth of 11% in 2021, reporting a $2.988 billion income compared to $2.683 billion for 2020. On a GAAP basis, in 2021 the company obtained an operating margin of 26 percent. The outlook for 2022 projects a revenue growth of approximately 12%. In a prepared statement issued on occasion of the latest financial results conference call, Cadence’s CEO Anirudh Devgan provided some details about the results achieved by the company in 2021. Cadence’s digital full flow was adopted by more than forty-five additional customers during the year, and preexisting relationships with Oppo and Socionext were expanded. As for the machine learning-based Cerebrus solution, Devgan only mentioned the benefits obtained by some unidentified users: a “market shaping U.S automotive company” reduced the power consumption of a critical five nanometer SoC AI block by nearly ten percent in just two weeks; a “premier Asia Pacific systems company” reduced power of their four-nanometer design by ten percent with one-tenth the effort of manual optimization; a “marquee US semiconductor company” taped out their next generation SoC with a 5x productivity improvement on several critical blocks. In 2021, Cadence’s Verification business grew twenty percent year-over-year, fueled by what Devgan called “a record year for hardware.” Demand for Palladium Z2 and Protium X2 platforms “has greatly exceeded our expectations,” he said. More than half of customers purchased both platforms during the year, and the “hardware family” added over thirty new customers. Devgan also pointed out that 2021 was “an exceptional year” for Jasper formal verification platform, which added over forty new customers. Other details offered by Devgan include SK Hynix and Micron being among the adopters of Spectre FX FastSPICE; the addition of “nearly a hundred new logos (…) notably in Aerospace & Defense” following Cadence’s acquisitions of Numeca and Pointwise; and the growth of cloud-based solutions, now used by over 250 customers. Cadence also announced a strategic partnership with French company Dassault Systèmes, through which the Allegro platform has been have combined with Dassaults’ 3DExperience platform to create a ‘virtual twin’ experience that integrates capabilities for electronic and mechanical products. Read the rest of Cadence’s 2021 results; Intel Investor Meeting; China’s wafer capacity Intel to acquire Tower; AMD-Xilinx deal completed; Foxconn-Vedanta to make chips in IndiaFebruary 16th, 2022 by Roberto Frazzoli

Foundries and fabs are making news again this week, along with the completion of one of the mega-deals announced in 2020 (AMD-Xilinx). As for the one that did not go through (Nvidia-Arm), a recent press report suggest that an Arm IPO will probably mean SoftBank accepting a valuation below the $32 billion it paid for the company in 2016 – and well below the $60 billion expected from the transaction. Intel to acquire specialty foundry Tower Semiconductor Confirming rumors, on February 15 Intel announced it will acquire Israel-headquartered foundry Tower Semiconductor for approximately $5.4 billion. With this transaction, Intel aims to create a globally diverse end-to-end foundry offering, bringing together its advanced nodes and scale manufacturing with Tower Semiconductor’s specialty technologies. Tower specializes in the manufacturing of analog semiconductor solutions addressing multiple markets, including aerospace and defense. Its process platforms include SiGe, BiCMOS, mixed-signal/CMOS, RF CMOS, CMOS image sensor, non-imaging sensors, integrated power management (BCD and 700V), and MEMS. The company also provides design enablement and process transfer services. Tower Semiconductor owns two manufacturing facilities in Israel (150mm and 200mm), two in the U.S. (200mm), three facilities in Japan (two 200mm and one 300mm) which it owns through its 51% holdings in TPSCo and is sharing a 300mm manufacturing facility being established in Italy with STMicroelectronics. Nvidia abandons Arm deal; new Arm’s CEO; European Chips Act; Intel Foundry allianceFebruary 9th, 2022 by Roberto Frazzoli

In various ways, some recent governments’ decisions are contributing to shaping the future of the semiconductor industry. On the one hand, opposition from regulatory authorities around the world is forcing Nvidia to give up the acquisition of Arm; additionally – after the recent passing of the U.S. CHIPS Act – also the European Union is planning public financial support to new local fabs. The big picture includes Intel – also in the news this week for its foundry initiatives – that is likely set to benefit from public support for its future fabs. Nvidia gives up Arm acquisition; Arm to go public On February 7 Nvidia and SoftBank Group jointly announced the termination of the transaction whereby Nvidia would acquire Arm from SoftBank. As stated in a press release, the parties agreed to terminate the attempted deal because of “significant regulatory challenges preventing the consummation of the transaction”. In the same announcement, SoftBank also stated that Arm will now start preparations for a public offering within the fiscal year ending March 31. Some press and analysts’ comments are focusing on Arm’s ability to self-fund its growth through the stock market. EETimes recalls that – in a last attempt to rescue the deal – Arm released a document in January indicating it would face significant hurdles to growth as a standalone company if the acquisition fell through. Patrick Moorhead on Forbes, however, notes that for financial year ending March 31, 2022, Arm is forecasted to generate a record $2.5B revenue and $900M in adjusted EBITDA. According to Moorhead, this means that “Arm is actually very profitable” and this somewhat surprising revelation sheds new light on the IPO option. Read the rest of Nvidia abandons Arm deal; new Arm’s CEO; European Chips Act; Intel Foundry alliance Driverless vehicles; Samsung’s GAA; Vodafone-Intel collaboration; geopolitical tensions; chip shortageFebruary 2nd, 2022 by Roberto Frazzoli

Advancements in autonomous vehicles are in the news this week, along with several other topical issues such as new transistor architectures, 5G, AI acceleration, geopolitical tensions, and the automotive chip shortage. Driverless vehicles updates: Cruise, TuSimple On February 1st Cruise opened up its driverless cars in San Francisco to the public. Users can book a driverless ride – free, for now – from a sign-up page on the company’s website. Cruise is planning to ramp up the service as more cars are made available. In a blog post, Kyle Vogt, interim CEO, CTO, and co-founder, wrote that reaching this milestone will prompt SoftBank Vision Fund to invest an additional $1.35 billion in Cruise. Advancements also concern TuSimple, which has reportedly announced that its autonomous trucks have driven 550 miles (885 km) on public roads in Arizona without being manned by human drivers. The company reported that a total of seven fully autonomous runs have been completed on an 80-mile stretch between Phoenix and Tucson, adding that no humans intervened in the traffic flow or operated the truck remotely. Fully autonomous freight services will also be offered in other large US shipping areas, including Texas, by the end of year 2023. TuSimple claims to be the world’s first company to operate fully driverless heavy-duty trucks. Intel new fabs in Ohio; stacked forksheet transistor; Nvidia-Arm updates; low power devicesJanuary 26th, 2022 by Roberto Frazzoli

The USA was definitely the center of the action last week with major announcements from Intel and Microsoft – spanning tech areas as diverse as fab construction and game development. Let’s start with Intel, while the Microsoft news can be found in our Acquisition paragraph. Intel to build two new fabs in Ohio Intel has announced plans for an initial investment of more than $20 billion in the construction of two new chip factories in Licking County, near Columbus, Ohio. In addition to providing capacity for Intel’s own products, these new factories will support the company’s new foundry business. The initial phase of the project is expected to create 3,000 Intel jobs and 7,000 construction jobs, and to support tens of thousands of additional local long-term jobs across the ecosystem. Spanning nearly 1,000 acres, the site can accommodate a total of eight fabs – as well as support operations and ecosystem partners. Intel stated that the total investment in the site could grow to as much as $100 billion over the next decade, making it one of the largest semiconductor manufacturing sites in the world. “The scope and pace of Intel’s expansion in Ohio, however, will depend heavily on funding from the CHIPS Act,” said Keyvan Esfarjani, Intel senior vice president of Manufacturing, Supply Chain and Operations. Construction is expected to begin late in 2022, while production is expected to come online in 2025. As part of Intel’s announcement, Air Products, Applied Materials, LAM Research and Ultra Clean Technology have indicated plans to establish a physical presence in the region. “The Columbus Dispatch” daily newspaper has a story on how Ohio won the bid by Intel. The article quotes a letter from Intel CEO Pat Gelsinger to the Ohio governor, saying “Ultimately, we hope to establish the largest semiconductor manufacturing site on the planet.” Vertical FET; emerging memories; TSMC’s capex; DAC figuresJanuary 19th, 2022 by Roberto Frazzoli

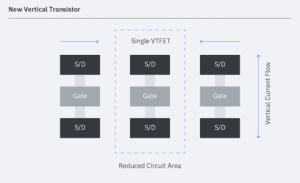

Later this year the industry will celebrate the tenth anniversary of the publication of AlexNet, widely considered the starting point of the current neural network boom. But another celebration took place recently: the fiftieth anniversary of the microprocessor. The magazine “IEEE Micro” has devoted a special issue to this event, hosting – among others – an article from Federico Faggin telling the story of the Intel 4004. EETimes also turned fifty recently, and veteran semiconductor analyst Malcolm Penn celebrated this anniversary by contributing three articles on the history of Silicon Valley: here are Part One, Part Two and Part Three. Let’s now quickly catch up on some of the news updates from December and early January. IBM and Samsung develop the vertical FET IBM and Samsung Electronics have jointly announced a new vertical transistor architecture called VTFET that promises further scaling beyond nanosheet. As explained in this blog post, vertically orienting the current flow removes the horizontal constraints to gates, spaces and contacts dimensions. In this way, the Contacted Gate Pitch can be scaled while maintaining healthy size for all these features. Specifically, the VTFET allows to use larger source/drain contacts to increase the current on the device; the gate length can be selected to optimize device drive current and leakage; and the spacer thickness can be independently optimized for lower capacitance. Another key VTFET feature is the ability to use shallow trench isolation for adjacent circuits, to achieve a Zero-Diffusion Break (ZDB) isolation, with no loss of active-gate pitches. By comparison, the density of conventional lateral-transport FET circuitry is affected by double or single-diffusion breaks required for circuit isolation, which affects the ability to further shrink. Read the rest of Vertical FET; emerging memories; TSMC’s capex; DAC figures 2021 Year in ReviewJanuary 12th, 2022 by Roberto Frazzoli

Let’s start 2022 by quickly recapping some of the major events and trends of 2021, which was another year of the so-called ‘silicon renaissance’ era – and, unfortunately, another year of Covid-19 pandemic. Record numbers, chip shortage, new fabs, geopolitical tensions As we all know, the semiconductor industry and its ecosystem thrived in 2021, due to strong demand from multiple end markets. In fact, the demand exceeded the global fab capacity, generating a severe chip shortage that especially hit carmakers. According to market research firm Omdia, in the third quarter of 2021 the semiconductor market surpassed $150 billion. Record numbers were also reported by the Electronic System Design Alliance for the EDA industry, and by Semi for the equipment and material market. As for this latter area, 2021 was an exciting year because of several announcements related to the planned construction of new fabs, such as Samsung’s plant in Texas or Intel’s factories in Arizona. Unfortunately, geopolitical tensions also increased in 2021, with China vowing to pursue reunification with Taiwan. Imperas targets RISC-V verificationDecember 16th, 2021 by Roberto Frazzoli

With its new ImperasDV solution, the company aims at enabling all RISC-V developers to accomplish the complex task of processor IP verification more efficiently “The greatest migration in verification responsibility in the history of EDA,” from processor IP vendors to SoC designers: this, according to Imperas Software, is the challenge facing SoC development teams as they take advantage from RISC-V customization capabilities. One of the reasons for the success of RISC-V is undoubtedly the possibility for any SoC developer of adding some degree of customization to the basic instruction set architecture, while saving the processor compatibility with the RISC-V ecosystem of supporting tools and software. The other side of the coin, however, is a heavier verification burden on the SoC development team: as opposed to an off-the-shelf processor IP which is pre-tested by the vendor, a customized processor needs to be verified by whom performed its customization. Addressing this challenge, Imperas Software has recently launched ImperasDV, an integrated solution for RISC-V processor verification. This new product is the main subject of the video interview that Larry Lapides, Vice-President at Imperas Software, has recently given to EDACafe’s Sanjay Gangal. In this article we will take a closer look at ImperasDV, adding a few details to the video interview content. We will also briefly discuss another major part of Imperas’ product offering, virtual platforms for embedded software development – along with the promotion of open model library availability through the Open Virtual Platforms (OVP) industry consortium. Based near Oxford, UK, with offices in Silicon Valley and Tokyo, Imperas software was founded in 2008 by Simon Davidmann, an EDA veteran.

|

|

|

|||||

|

|

|||||

|

|||||