EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Synopsys’ big data solution; GenAI-specific acceleration; lower cost SWIR sensors; MediaTek’s 3nm chipSeptember 8th, 2023 by Roberto Frazzoli

The Chinese government will reportedly launch an additional state-backed investment fund aiming to raise about $40 billion for the domestic semiconductor industry. According to Reuters, individual Chinese chipmakers that have already received state subsidies include GTA Semiconductor, specializing in automotive applications, which was reportedly granted over $1.8 billion. Other updates related to the US-China tensions include the growing capability of Chinese chipmakers: more than half, maybe two-thirds of the chips contained in Huawei’s new high-end smartphone are made in China, according to Canadian reverse engineering firm TechInsights. Lastly, the Chinese government has reportedly told state employees to stop using their iPhones at work. Synopsys unveils its big data analytics solution Synopsys has extended its Synopsys.ai full-stack EDA suite with a comprehensive AI-driven data analytics continuum for every stage of chip development, leveraging the vast amounts of heterogeneous design data generated by EDA, testing, and IC fabrication tools – such as timing paths, power profiles, die pass/fail reports, process control, or verification coverage metrics. The AI-driven Synopsys EDA Data Analytics (.da) solution includes: Synopsys Design.da to perform deep analysis of data, to uncover PPA opportunities; Synopsys Fab.da to store and analyze large streams of fab equipment process control data, to maximize product quality and fab yield; Synopsys Silicon.da to collect petabytes of silicon monitor, diagnostic, and production test data from test equipment, to improve chip production metrics.

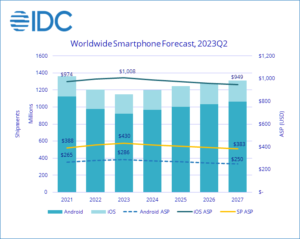

D-Matrix’s GenAI inference solutions attract investors Santa Clara-based AI chip startup d-Matrix has closed $110 million in a Series-B funding round led by Singapore-based investment firm Temasek. The group of investors reportedly includes Microsoft. The goal of the fundraise is to enable d-Matrix to begin commercializing Corsair, what the company claims is the world’s first Digital-In Memory Compute (DIMC), chiplet-based inference compute platform. As explained in this white paper, d-Matrix’s solutions are specifically targeted at generative AI inference, and aim to reduce costs by orders of magnitude. The company’s technology is based on a new multiplying element using a 6T SRAM bit cell with four additional transistors. However, unlike traditional SRAM solutions, d-Matrix activates all word lines simultaneously. This technique reduces the memory footprint and relieves memory bandwidth pressure, helping to save power while enhancing the performance of transformer models. Additionally, the d-Matrix solution keeps weights loaded in SRAM to rapidly compute multiple inferences without transferring data over the system bus. IFS-Tower agreement Just a few days after scrapping their planned merger, Intel Foundry Services and Tower Semiconductor have announced an agreement where Intel will provide Tower foundry services and 300mm manufacturing capacity. Under the agreement, Tower will utilize Intel’s manufacturing facility in New Mexico. Tower will invest up to $300 million to acquire and own equipment and other fixed assets to be installed in the New Mexico facility, providing a new capacity corridor of over 600,000 photo layers per month. Intel will manufacture Tower’s 65-nanometer power management BCD (bipolar-CMOS-DMOS) flows, among other flows at Intel’s Fab 11X in Rio Rancho, New Mexico. Automotive sensor updates: indie, Tower-TriEye, imec Some recent technology advancements concern automotive sensors, in a broad sense. Indie Semiconductor has launched what it claims is the world’s first commercial fully integrated 240 GHz radar front-end silicon transceiver. The higher frequency-enabled superior precision of 240 GHz radar is being leveraged for new vehicle dynamics and monitoring applications, including assessment and control of air spring-based suspension settings, real time road surface quality and hazard assessment to dynamically adapt ride quality, and even fine grade monitoring of gas tank levels. Two new SWIR (short-wave infrared) solutions – both CMOS-based and aiming to reduce costs – have recently been announced, potentially enabling cars to see through fog or smoke. Tower Semiconductor and TriEye have released a SWIR sensor for the automotive ADAS and industrial markets, featuring a 1.3Mp 7um pixel array. The new device utilizes Tower’s BSI Germanium photo-diodes on silicon using a unique pixel-level electrical connection in a wafer stacking process, allowing a monolithic CMOS based solution. According to TriEye, while existing SWIR sensors are inherently very expensive, this new SWIR CMOS-based solution provides high performance at low cost. Belgian research institute imec has successfully integrated a pinned photodiode structure in thin-film image sensors, achieving superior noise performance. To obtain this result, a SWIR quantum-dot photodetector was monolithically hybridized with an indium-gallium-zinc oxide (IGZO)-based thin-film transistor into a pinned photodiode pixel. This array was subsequently processed on a CMOS readout circuit to form a superior thin-film SWIR image sensor. Samsung’s 32-gigabit DDR5 DRAM Samsung Electronics has developed the industry’s first 32-gigabit DDR5 DRAM using 12-nanometer process technology. The solution will enable DRAM modules of up to 1-terabyte. Samsung points out that previously DDR5 128GB DRAM modules manufactured using 16Gb DRAM required the Through Silicon Via (TSV) process, whereas the new 32Gb DRAM allow to produce the 128GB module without TSVs – while also reducing power consumption by approximately 10% compared to 128GB modules with 16Gb DRAM. Mass production of the new 12-nanometer 32Gb DDR5 DRAM is scheduled to begin by the end of this year. MediaTek’s first 3nm chip MediaTek has successfully developed its first chip using TSMC’s leading-edge 3nm technology, taping out the flagship Dimensity system-on-chip. MediaTek’s first flagship chipset using TSMC’s 3nm process is expected to empower smartphones, tablets, cars and various other devices starting in the second half of 2024. Smartphone shipments to reach lowest volume in a decade Worldwide smartphone shipments are forecast to decline 4.7% year over year in 2023 to 1.15 billion units, the lowest volume in a decade, according to International Data Corporation. This is a downward revision from IDC’s previous forecast of -3.2%, driven by a weaker economic outlook and ongoing inflation. IDC expects the market to recover in 2024 with 4.5% year-over-year growth followed by growth in the low single digits through the remainder of the forecast, resulting in a five-year compound annual growth rate of 1.7%. Events IAA Mobility 2023 is running until September 10 in Munich, Germany. The FPGAworld Conference 2023 will take place in Stockholm, Sweden, on 12 September and Copenhagen, Denmark, on 14 September. |

|

|

|||||

|

|

|||||

|

|||||