EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Leveraging EDA data to improve productivity and PPA: the Cadence JedAI platformNovember 14th, 2022 by Roberto Frazzoli

A closer look at the recently announced ‘Joint Enterprise Data and AI’ infrastructure, an AI-driven, big data analytics environment Announced last September 13, the JedAI platform is the new Cadence AI-driven, big data analytics environment, meant to be tightly integrated with the company’s recently introduced AI-based platforms: Verisium for verification, Cerebrus for implementation, and Optimality for system optimization. Features and benefits of JedAI were described by Rod Metcalfe – Product Management Group Director, Digital and Signoff Group at Cadence – in the video interview he recently gave to EDACafe’s Sanjay Gangal; building on that interview, in this article we will add a few more details with the help of a Cadence white paper – along with the answers provided by Rod and by Kam Kittrell – vice president, Product Management in the Digital & Signoff Group at Cadence – to some additional questions.

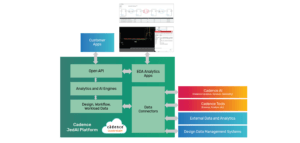

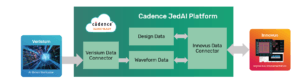

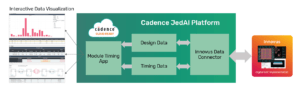

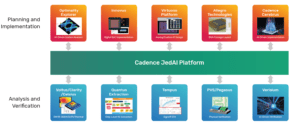

The value of EDA data generated during the design process A key concept behind JedAI is that the large amount of EDA data generated during the iterative design and verification flow is a valuable asset, as it hides many useful insights and learnings. However, according to Cadence, today just a small part of this information gets reviewed by the engineering teams as the design progresses, while the majority is simply deleted to create disk space for the next project. The JedAI platform aims to prevent this waste and make good use of the data, as Metcalfe explained: “When somebody designs a typical system on chip today, an enormous amount of data is generated, which should be very valuable, but today it’s not really being used in a systematic and productive way. Some people use spreadsheets – I’m sure we’ve all done it, loaded some data into a spreadsheet, taken a look at the results – but really that’s not working anymore. So the idea behind the Cadence Joint Enterprise Data and AI platform is providing a scalable and secure infrastructure to store and manage all this EDA data that is generated during a typical design process. [JedAI] also includes some artificial intelligence data analytics,” he continued, “so we can process the data and provide insights for the design teams about what could be improved.” The challenge of storing and processing heterogeneous EDA data However, storing and processing EDA data in general-purpose environments is difficult, due to the unique nature of the chip design process which leads to the generation of a wide range of heterogeneous, structured and unstructured information. “If you look at EDA type data, it’s fundamentally unstructured,” Metcalfe observed. “There are all kinds of different data: for example, we have shape information that’s used in the final GDS database, things like polygons and rectangles. At the other end of the spectrum we have things like netlists and RTL files, which are completely textual; and then there’s sort of log files, analysis reports, TCL scripts that manage the whole flow. This wide variety of data is actually very challenging. The JedAI platform has been optimized to support this unstructured EDA data, and it’s surprisingly difficult to do that. Anybody who’s tried to build their own environment in this area has rapidly found that this unstructured data presents a few challenges.” According to Cadence, these challenges called for the construction of a new platform from the ground up, capable of supporting different types of EDA information in their different forms. Three types of EDA data “We’ve kind of split the EDA data into three categories,” Metacalfe explained. “You have the design data: this is the netlist, the RTL, the timing constraints, floorplans, waveform information from verification, for example. Then we have workflow data: this is really the methodology that’s used to create the design, the tools that are used, when they’re used, what the general flow is to create the chip itself. And then finally we have workload data: information about what kind of compute resources were required to create the design, what kind of memory requirements, what kind of run time.” The Cadence white paper provides more details about the data collected by the JedAI platform. Design data includes functional verification results, physical layout shapes, analysis reports (area, timing, power, voltage), design specifications (RTL, netlist, SDC, UPF). Workload data refers to a set of application jobs, and includes metadata about the inputs to each job and dependencies between them. Examples of application jobs are all the Cadence Xcelium, Jasper, and Palladium runs in a Verisium Manager test plan; all the Cadence Spectre runs launched by Liberate cell characterization; all the Cadence Genus and Innovus runs launched by the Cadence Cerebrus Intelligent Chip Explorer. Data formats supported range from binary files – such as GDS physical shapes and verification waveforms – to text files – such as LEF/DEF, analysis reports, and tool logs. The JedAI platform provides dedicated data connectors to Cadence solutions to ingest this wide variety of data sources. General purpose open data connectors are also provided, so designers can import third-party data if necessary. “It’s a very open system,” Metcalfe observed. “You can bring in industry standard format files like a comma separated value file. We encourage designers to bring in their own data and start doing some analytics on that also.” From ‘single-run, single-engine’ to ‘multiple runs of multiple engines’ But what is the value of all this data? How can it be mined to extract useful insights and learnings? A key concept here is the ability to capture the evolution of a design across its versions, and the experience of the design team across many projects. As Metcalfe put it, “One of the nice things about the JedAI platform is it can store data through a period of time, so we have historical data: not just one version of one design, but many versions of many designs can be stored. So we can start doing analytics based on all this historical data to predict the outcome of the future design.” The ability to compare different design versions and the results from different tools is what – according to Cadence – enables “a generational shift” in EDA: from single-run, single-engine algorithms, to algorithms that leverage big data and artificial intelligence to optimize multiple runs of multiple engines across an entire SoC design and verification flow. Examples provided by Cadence – when describing Verisium, which is built on top of JedAI – are “leveraging data from simulations yesterday or last week to improve the efficiency of debugging failures from today, or improving the effectiveness of the simulations tomorrow. Similarly, leveraging data from Jasper formal runs to help debug Xcelium simulation failures.” Standard-based APIs enabling the creation of analytic apps These insights are extracted using big data analytics and AI-based techniques, as Metacalfe explained: “Along with this workflow and workload and design data that we’ve stored, there’s a whole bunch of different analytic engines built into JedAI. And these are very much based on some artificial intelligence research we’ve been doing. These analytic engines can be accessed through some industry standard procedural interfaces, so APIs in effect. Built on these APIs, we can create apps which plug in to the Cadence JedAI platform, and using these apps we can do lots of different analytic type work. These apps can be created using industry standard formats, for example, we support Python, Jupyter Notebook, as well as a whole bunch of HTML protocols like REST. So it’s very easy to access the analytics engines using these APIs. Clearly, Cadence will be creating apps; we already have a few ready and we’ll be developing more in future. But more importantly, design teams can create their own apps also. So if there’s a certain type of analytics they want to do as part of the design process, they can create their own apps and they can use that directly with JedAI. So, it’s an open system – because really Cadence can’t create every possible app that every design team might want to use,” Metcalfe said. Using design data to improve PPA and reduce runtime Let’s now move to providing some examples of how – according to Cadence – the JedAI platform makes it possible to use the EDA data to obtain different benefits. As for improving a chip’s power-performance-area figures, the platform enables users to compare metrics across different versions of the same design and/or multiple designs, providing recommended actions to improve PPA and increase verification coverage. According to Cadence, JedAI can also deliver productivity benefits – through its integration with Cerebrus. This implementation system generates a lot of design metrics data and ML models, which the JedAI platform can utilize in various ways. For example – based on enormous quantities of historical Cerebrus ML model data, and using AI-driven analytics – the JedAI platform can predict and generate a customized ML model for future designs, reducing the run time for Cerebrus to generate an optimized design. Using verification data to increase coverage and productivity The JedAI platform is the key underlying technology enabling the recently announced Cadence Verisium AI-driven verification platform. Therefore, in this case the benefits claimed for JedAI are basically the ones Cadence already described for Verisium. Using the Verisium platform, all verification data – including waveforms, coverage reports, and log files – are brought together in the JedAI platform. Machine learning models are built and other proprietary metrics are mined from this data to enable a new class of tools that improve verification efficiency. According to Cadence, the Verisium apps – AutoTriage, SemanticDiff, PinDown, WaveMiner, and Debug – allow to optimize verification workloads, boost coverage and accelerate root cause analysis of bugs, improving overall verification productivity. “Verisium already uses JedAI. You can think about Verisium as a very high-level app on top of JedAI,” Metcalfe pointed out. Using workflow data to improve design methodologies Leveraging workflow data basically means keeping track of the tools and methodology used during all SoC designs, in order to enable comparisons across multiple projects to distill best practices. According to Cadence, JedAI’s integrated workflow management capability allows users to efficiently capture chip design methodologies and automatically transfer design data between projects through data connectors. Using workload data to optimize resource utilization Lastly, the historical workload data collected by the JedAI platform can be used to predict the resource requirements of new jobs, select the most appropriate machine for each job, and optimize the overall scheduling of the jobs. According to Cadence, this will help increase server farm utilization on-premises or cut compute costs in the cloud. “We can start doing some prediction technology,”, said Metcalfe. “If you are starting a new design which looks similar to something you’ve done in the past, then the JedAI platform can start saying: hey, look, you should allocate this compute resource for this length of time for your new project. (…) I think that will be very beneficial for engineering teams, because at the moment it’s very much a guessing game in terms of what types of resources you’re going to need for the next design,” he added. Application example: power optimization Cadence has provided an example of how the JedAI platform – in connection with Verisium and Innovus – can enable better power optimization and improve engineering productivity. The Verisium verification platform can store VWDB waveform data in JedAI, which can then be utilized by the Innovus Implementation Solution to annotate accurate net activity information. This allows the GigaOpt engine to reduce total power on the highly switching parts of the netlist. Using the Verisium-to-JedAI data connector, the VWDB simulation waveforms are streamed into JedAI. To allow the correct design workload scenario to be identified, the verification engineer can also create metadata markers in JedAI to identify windows of time in the waveform that should be used for power optimization. Innovus then reads the simulation waveform data directly from JedAI using the relevant data connector. The net activity information is annotated within Innovus so the power analysis engine can compute total power correctly, which in turn will drive GigaOpt activity-aware power optimization, reducing the total power of the final design for the identified workload scenario. “First, we need to be able to share data across the whole design flow,” Metcalfe commented. “At the moment the design methodology is very segmented, but sharing data – for example, between the verification environment and the implementation part of the flow – is very useful, because the verification results should be able to drive implementation. One of the advantages of the JedAI platform is to enable data to be shared throughout the flow, and that will just be a huge ease of use for design teams.” Application example: RTL module timing criticality analysis Another application example offered by Cadence concerns a JedAI app that – in connection with Innovus – can enable RTL module timing criticality analysis. As recalled in the white paper, an SoC is created from a hierarchy of RTL modules, each one connected to other parts of the chip using input and output ports. The RTL team needs to understand the timing criticality of these connections, but this information is difficult to extract from a static timing analysis report. The JedAI platform includes an analytics tool that, using the Innovus data connector, can generate a module-based timing criticality report, showing a matrix of modules that communicate, and the associated port timing. This analysis can be visualized using JedAI’s web-based graphical interface. As the JedAI platform can store many revisions of the SoC design data, it is possible to show how the RTL port timing changes based on different revisions of the source RTL, which enables the RTL designers to understand which RTL changes have been effective for improving timing, both within each module and across all the module boundaries. “That is very useful.” Metcalfe pointed out, “because not only can we do that on a particular design and a particular version of that design, but we can do it historically. The JedAI platform can process all the different design versions that become available and quickly identify if a particular version of the RTL caused a timing difficulty in one of the blocks or across the block boundaries. This is very difficult to do unless you have an integrated platform like JedAI, because you can’t really store the historical data very easily.” Developing a cross-Cadence infrastructure Cadence describes the JedAI platform as the solution that unifies its computational software innovations in data and AI across Verisium verification, Cerebrus implementation, and Optimality system analysis – supporting the company’s ‘Intelligent System Design’ strategy. Let’s take a closer look at this strategy and at the relationships among all these products. “The Cadence JedAI platform has been in development for the past few years – explained Kam Kittrell – to support the roadmap for our AI products such as the Cadence Cerebrus Intelligent Chip Explorer and Optimality Intelligent System Explorer. The Cadence JedAI platform expands the effectiveness of our AI productivity improvement tools. (…) Our AI optimization tools already identify trends and make decisions. The Cadence JedAI Platform expands this capability. For example, Cadence Cerebrus can work on optimizing a particular block. Cadence Cerebrus with Cadence JedAI platform can work on optimizing an entire subsystem while making intelligent decisions on compute resource allocation,” Kittrell pointed out. “The Cadence Cerebrus and Optimality Explorer products can be used without the Cadence JedAI platform,” Metcalfe clarified; and in fact both these products were announced before JedAI. “But some of the more advanced AI features – he added – are only available if the Cadence JedAI platform is installed. The Verisium Artificial Intelligence-Driven verification platform requires the Cadence JedAI platform infrastructure, which is included as part of the product delivery.” “The plan is that all the different Cadence technologies start using JedAI. (…) In future, a lot of the other [Cadence] products will certainly be integrated. The intention is this becomes really a cross-Cadence infrastructure,” Metcalfe added. Disk resources As we saw earlier, a key concept behind JedAI is leveraging the large amount of EDA data generated during the design and verification flow, instead of deleting it to create disk space for the next project. Will big data analytics in EDA call for more storage and processing resources? According to Metcalfe, the benefits will be worth the effort: “By using the Cadence JedAI platform, designers will quickly appreciate the value of data being generated during a typical chip design flow,” he maintained. “The Cadence JedAI platform does need to store all this design data, which will require some disk resources, but with easy access to cloud-based compute and storage facilities, it is now much easier to manage these requirements efficiently. Ultimately design teams need to deliver final system-on-chip devices as quickly as possible, and the Cadence JedAI platform enables better productivity by utilizing data,” Metcalfe concluded. Besides the already mentioned white paper, resources on JedAI made available by Cadence include a blog post by Venkat Thanvantri, and two videos featuring Yong Liu and Venkat Thanvantri respectively. Categories: EDACafe Editorial, Video Interview |

|

|

|||||

|

|

|||||

|

|||||