EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. New fab rumors; TSMC’s innovations; low-temperature 3D chip bonding; new optical microphoneJune 24th, 2022 by Roberto Frazzoli

The so-called metaverse now has its standardization initiative: called Metaverse Standards Forum, it brings together a few dozen founding members including Meta (Facebook), Microsoft and Nvidia – but, as noted by Reuters, the member list currently does not include Apple. However, “the Forum is open to any company, standards organization, or university at no charge,” says the announcement press release, so never say never. Let’s now move to our usual news round-up, that this week includes a couple of interesting academic works. Quick EDA updates Keysight’s PathWave RFPro, integrated with the Synopsys Custom Compiler design environment, is enabled to support TSMC’s newest N6RF Design Reference Flow. Pulsic has added new features to its Unity product. Among them, Unity Chip Planning technology now can handle incremental floorplans; and the embedded integrations with Cadence Virtuoso and Synopsys Custom Compiler allow users to access Unity directly from these systems. Cadence’s Design IP offering has already achieved over twenty design wins in TSMC’s 5nm process technology, with multiple first-pass silicon successes. Xpeedic has recently released its latest RF EDA/Filter Design Platform 2022.

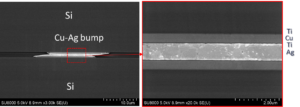

Fab updates Japan will reportedly work with the U.S. to launch a domestic manufacturing base for 2-nanometer semiconductors as early as 2025. Tokyo and Washington will provide support under a bilateral technology partnership. Japanese and U.S. businesses could jointly establish a new company, or Japanese corporations could set up a new manufacturing hub. Japan’s Ministry of Economy, Trade and Industry will partially subsidize the R&D cost as well as capital expenditures. Joint research will start this summer at the earliest, and a research and mass production center will be established between 2025 and 2027. GlobalFoundries and STMicroelectronics are reportedly in talks to build a fab in France together with the help of government funds from the EU Chips Act. The new French factory could focus on energy efficient chips with advanced technology. As noted by Bloomberg, in April GlobalFoundries and STMicroelectronics – together with Soitec and the CEA research hub – announced the start of a collaboration to develop the next generation of FD-SOI technology. TSMC’s innovations On occasion of its 2022 North America Technology Symposium, recently held in Santa Clara, CA, TSMC showcased its newest innovations. The N3 technology, set to enter volume production later this year, will feature the TSMC FinFlex options: a choice of different standard cells with a 3-2 fin configuration for performance optimization, a 2-1 fin configuration for power efficiency and transistor density, and a 2-2 fin configuration for a balance between the two. The upcoming N2 technology, scheduled to begin production in 2025, will feature nanosheet transistor architecture to offer a 10-15% speed improvement at the same power, or 25-30% power reduction at the same speed, over N3. The company also announced an expansion of its ultra -low power platform, and showcased two customer applications of the TSMC-SoIC chip stacking solution: a SoIC-based CPU employing Chip-on-Wafer (CoW) technology to stack SRAM as a Level 3 cache, and an intelligence processing unit stacked on top of a deep trench capacitor die using Wafer-on-Wafer (WoW) technology. At the symposium, TSMC reportedly said it will have the ASML’s high-NA EUV litho equipment in 2024, clarifying that the foundry would not be ready to immediately use it in production; initially the high-NA system will be used mostly for research with partners. Chiplet updates: UCIe, eFPGAs The UCIs standard for interoperability of chiplets within a package keeps gaining momentum. Taiwan-based GUC has joined the UCIe consortium as Contributor Member and is now the member of six working groups. GUC points out that its GLink die-to-die connection solution for TSMC CoWoS and InFO already supports most of UCIe 1.0 digital and analog functionality. Avery Design Systems, a provider of functional verification solutions, has announced comprehensive support for UCIe, including models and test suites that support pre-silicon verification of systems using UCIe. As part of the support for the standard, Avery has joined the UCIe consortium. The chiplet approach extends to eFPGAs: QuickLogic and eTopus have come up with what they claim is the industry’s first “disaggregated eFPGA-enabled chiplet template solution”. Based on QuickLogic’s Australis eFPGA IP Generator and chiplet interfaces from eTopus, the disaggregated solution will be available initially as a configurable IP, and eventually as Known Good Die chiplets. Silver-based, low-temperature, pressureless 3D chip bonding Researchers at Osaka University have demonstrated a new method for bonding copper bumps – in 3D chip stacking – that works at low temperatures and does not require external pressure. In this new method, silver is first sputtered at room temperature onto the two copper bumps to be bonded. Then, heat is applied to anneal the silver layers – at just 180 °C – leading to surface roughening. As a result, bonding can be accomplished without applied pressure. Permanent connections as small as 20 micrometers could be realized in just ten minutes this way. Researchers said the bonds were able to withstand over one thousand cycles of thermal shocking from -55 to 125 °C. The study, “Ag-Ag direct bonding via a pressureless, low-temperature, and atmospheric stress migration bonding method for 3D integration packaging,” was presented at the IEEE Electronic Components and Technology Conference (ECTC).  (Right) Cross-sectional image of bonded Cu-Ag bump, (Left) Magnified view of the interface of the bonded Cu-Ag sample. Source: “Research at Osaka University” website New optical microphone uses ordinary cameras to capture sound A research team from Carnegie Mellon University has developed a new type of “optical microphone” – that is, a camera-based system that enables the reconstruction of an audio signal from the image of the vibrating surface that generates is. As opposed to earlier systems, the new solution does not require an expensive high-speed camera; it can sense vibrations at high speeds (up to 63kHz), for multiple scene sources at once, using sensors rated for only 130Hz operation. The new method employs a laser beam to illuminate the vibrating surface, and captures the scene with two cameras equipped with rolling and global shutter sensors, respectively. One of the key benefits of an optical microphone, compared to its conventional counterpart, is its ability to capture a single sound source with no interference from surrounding sources: for example, a single musical instrument in an orchestra, or a single machine – for predictive maintenance – in a factory floor. Acquisitions Applied Materials has acquired Picosun, a privately held semiconductor equipment company based in Espoo, Finland. Picosun is an innovator in atomic layer deposition (ALD) technology, primarily for specialty semiconductors. Qualcomm has acquired Texas-based Cellwize Wireless Technologies, a provider of mobile network automation and management solutions for 5G Radio Access Networks (RAN). Upcoming events TechInsights’ “Memory Process and Integration Challenges: DRAM & NAND” webinar will be held on July 5 and 6. Si2 Annual Member Meeting and Reception will take place on July 11 in San Francisco. For more events, see the EDACafe event calendar. |

|

|

|||||

|

|

|||||

|

|||||