Geopolitical issues keep making news: a team of U.S. investors, scientists, operators, and national security experts has founded America’s Frontier Fund (AFF), described as “the nation’s first non-profit strategic investment fund focused on building and scaling breakthrough deep-tech companies and platforms for the national interest.”. Led by CEO and co-founder Gilman Louie, AFF intends to counter “authoritarian nations” that “are committed to out-spending and out-innovating the U.S. to gain military and economic superiority.” The fund’s initial areas of focus will include microelectronics, artificial intelligence, new materials, quantum sciences, next generation networks (5G/6G), advanced manufacturing, and synthetic biology. Let’s now move to other news updates, this week with a significant presence of European research centers.

Imec demonstrates backside power delivery with buried power rails

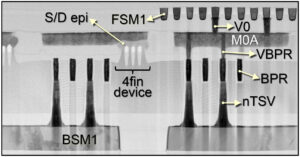

Belgian research institute Imec has demonstrated a routing scheme for logic ICs with backside power delivery enabled through nano-through-silicon-vias (nTSVs) landing on buried power rails (BPRs). The BPRs connect to scaled FinFET devices whose performance was not impacted by backside wafer processing. The novel routing scheme with decoupled power and signal wiring acts as a scaling booster for future logic technologies (2nm and beyond), as the nTSVs land on BPRs with tight overlay control and are implemented at a tight pitch of 200nm without consuming any area of the standard cell. The solution also offers a system performance benefit by improving the power delivery, as it reduced IR voltage drop. Additionally, Imec demonstrated a performance boost by implementing a 2.5D MIMCAP (metal-insulator-metal capacitor) in the backside serving as a decoupling capacitor. Backside power delivery – using the back side of the wafer to route power lines, in order to alleviate routing congestion on the front side and reduce IR voltage drop – can be implemented in different ways; Imec believes that combining it with buried power rails is the most promising implementation scheme.