EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Nvidia to acquire Arm; photonic design; 300M gate prototyping system; 4Gbps memory interface; wire aggregation; ML on Cortex-M0September 14th, 2020 by Roberto Frazzoli

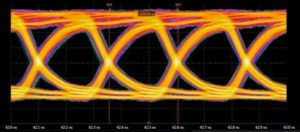

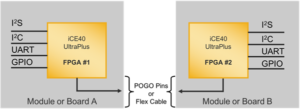

Nvidia-Arm news are obviously taking center stage this week, but several interesting updates also deserve attention in areas such as EDA, prototyping, embedded systems, events, acquisitions and more. Nvidia-Arm deal Rumors have been confirmed: GPU market leader Nvidia will acquire Arm from Japanese conglomerate company SoftBank in a transaction valued at $40 billion, what is considered the largest semiconductor deal ever. The official announcement stresses the powerful pairing that brings together Nvidia’s AI computing platform with Arm’s large footprint in many diverse end products and industries, adding that Arm R&D resources in the UK will get a boost as part of the deal. In its statement, Nvidia pledges that “Arm will continue to operate its open-licensing model while maintaining the global customer neutrality that has been foundational to its success.” It remains to be seen how Arm licensees and governments’ regulating authorities will react to the news. The new situation could also potentially change the competition landscape for Risc-V open-source ISA. Synopsys to make photonic design more accessible According to Synopsys, widespread implementation of photonic integrated circuits has, until now, been impeded because many design tools were intended for electronics rather than photonics. As a result, photonic design has largely been the domain of experts who could build their own tools or repurpose a disparate toolset. Now, with the introduction of its OptoCompiler solution, Synopsys aims at bridging the gap between photonic experts and IC designers to make photonic design more accessible. OptoCompiler capabilities include support for electronic-photonic co-design and for hierarchical design; ability to use dedicated native photonic simulators; features such as native optical port and net support, assisted waveguide routing, auto-alignment of photonic circuits, and curvilinear layout synthesis; support for industry standards such as Python, TcL and OptoDesigner. A 300 million gate FPGA-based prototyping system Shanghai-headquartered company S2C has introduced a new 300 million equivalent ASIC gate prototyping solution based on four Intel Stratix 10 GX 10M FPGA devices. Called Quad 10M Prodigy Logic System, the solution relies on the combined hardware resources of the four Stratix chips: 40.8 million logic elements, 1,012Mb memory, 13,824 DSP blocks, 4,608 high-performance I/Os for inter FPGA connections and daughter cards, 160 high-speed transceivers that can run up to 16Gbps. The Quad 10M Prodigy Logic System is equipped with a control module that has built-in debug hardware to enable high-performance deep trace capability for multiple FPGAs without extra peripherals, and offers enhanced partitioning tools that can perform automatic intra-FPGA partition. New Rambus 4.0 Gbps memory interface In July, SK hynix announced full-scale mass-production of its HBM2E high-speed DRAM operating at 3.6 Gbps. Now a fast-enough interface has been announced by Rambus to take advantage of this memory, forming a solution that can deliver 460 GB/s of bandwidth. Consisting of a fully integrated PHY and controller, the Rambus interface achieves a 4 Gbps performance. Rambus teamed with SK hynix and Alchip to create the solution using TSMC’s N7 process and CoWoS (Chip-on-Wafer-on-Substrate) packaging technologies. Reducing board-to-board wire count with FPGA-based wire aggregation Board-to-board or module-to-module connections in embedded systems usually require several wires carrying I2C, I2S, UART and GPIO data streams. Consequently, these cabling involves bulky connectors that consume PCB space and add potential reliability issues to the system. Now Lattice is addressing this problem with a solution based on its iCE40 UltraPlus FPGA, a low-power and small-size device. Its Single Wire Aggregation (SWA) IP solution provides the hardware and software required to implement a single wire interface capable of aggregating multiple I2C, I2S, UART and GPIO data streams. According to Lattice, the solution does nor require any HDL coding experience, as the company offers pre-configured bitstreams for the FPGA device. Five aggregated I/O configurations are currently offered, with different combinations of signals. As an example, three I2C controller, two I2C peripheral, and 15 GPIO signals can be aggregated into one single wire. Machine learning on Arm Cortex-M0 and M0+ Qeexo (Mountain View, CA) has announced that its Qeexo AutoML automated machine learning platform now supports machine learning on Arm Cortex-M0 and Cortex-M0+ processors. With the term “automated”, Qeexo means that its platform takes care of many tasks involved in implementing a neural network-based machine learning solution, such as collection and labeling of training data, optimizations, model compressions, and hyper-parameter tuning. The Cortex-M0 processor, the smallest Arm processor available, powers sensors and microcontrollers from companies such as Arduino, Renesas, STMicroelectronics, and Bosch Sensortec. The Cortex-M0+ processor offers a further reduction of energy consumption with increased performance. Germany’s electronica show to take place as a virtual-only event Contrary to what was previously announced, this year’s edition of Munich’s electronica trade show will take place in a virtual-only format. The organizing company, Messe München, has motivated this decision citing “the far-reaching, worldwide travel restrictions in a large number of our exhibiting and visiting countries.” The virtual exhibition will be supplemented by a digital conference and supporting program. Individual lectures and discussion panels on trend topics such as automotive, embedded, IIoT, 5G, medical electronics and smart energy will be available online. Further information is expected shortly. Until recently, the electronica website displayed the floorplan of a “compact trade fair” planned for next November, occupying seven halls of the Munich exhibition center. Semicon Europa 2020, initially planned as a co-located physical event with electronica, will also be replaced by a digital forum, whose details have not been announced yet. Acquisitions EDA vendor Silvaco has completed acquisition of the assets of French company Coupling Wave Solutions (CWS), including IP, patents, and analysis technologies. CWS is a provider of tools for system-level interference analysis of complex SoCs that integrate analog, RF, and digital blocks. The acquisition expands Silvaco’s portfolio to address the growing need for RF SOI (Silicon on Insulator) substrate analysis to model and simulate noise interference in circuits used in 5G and IoT applications. Specifically, Silvaco will now offer the CWS products WaveIntegrity and SiPEX as part of its product portfolio. MaxLinear, a provider of radio frequency, analog, digital and mixed-signal integrated circuits, has completed the acquisition of NanoSemi, a Boston-based MIT spinoff providing intellectual property that utilizes machine learning techniques to enable higher throughput, lower energy connections for 5G and Wi-Fi base stations and smartphones. |

|

|

|||||

|

|

|||||

|

|||||