EDACafe Special Report: Signal Integrity and Power Integrity Challenges in High-Speed PCB Design

Part Two – Interview with Stephen Slater, Product Planning and Marketing Manager at Keysight Technologies

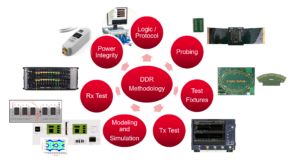

Signal integrity and power integrity issues are becoming increasingly challenging for designers of high-speed PCBs required by next generation applications – such as 5G – and new semiconductor devices – such as DDR5 memories. What are the key aspects that designers should consider? What are the capabilities of the tools offered by EDA vendors to address these issues? To answer these questions, EDACafe has interviewed experts from some of the major vendors in this specific market. Part two of our special report features an interview with Stephen Slater, product planning and marketing manager at Keysight Technologies. On occasion of the last DesignCon show, Keysight introduced what it claims to be “the world’s first design and test workflow solution that reduces product development time for Double-Data Rate Dynamic Random-Access Memory (DDR5 DRAM) systems.” This interview will therefore focus mainly on DDR5 and on Keysight’s PathWave solution.