The growing role of neural networks in chip design has been a recurring theme over the past few weeks, in speeches or announcements involving a number of different subjects. Meanwhile, the new golden age of innovative processing architectures continues, spurred by 5G requirements. Other recent news includes more EDA vendors end-of-year results, and acquisitions in the semiconductors industry.

Machine learning to improve place-and-route in chip design

Better placement and routing in much less time and, ultimately, a dramatic reduction of ASIC design time: this is what machine learning promises to the chip designer community. ML-powered place-and-route was one of the key points of Google’s Jeffrey Dean keynote speech at the recent ISSCC. In a paper packed of interesting insights and data about machine learning evolution, Dean addressed this issue with concepts that are bound to raise attention. According to Dean, “placement and routing is a problem that is amenable to the sorts of reinforcement learning approaches that were successful in solving games, like AlphaGo. (…) By having a reinforcement learning algorithm learn to ‘play’ the game of placement and routing (…), with a reward function that combines the various attributes into a single numerical reward function, and by applying significant amounts of machine-learning computation (in the form of ML accelerators), it may be possible to have a system that can do placement and routing more rapidly and more effectively than a team of human experts working with existing electronic design tools for placement and routing”, Dean maintains. Google has been exploring these approaches internally, obtaining promising results; some of them have been described in this EETimes article. In his paper, Dean cites more potential benefits that chip design could get from machine learning: “The automated ML based system also enables rapid design space exploration, as the reward function can be easily adjusted to optimize for different trade-offs in target optimization metrics. Furthermore – he continues – it may even be possible to train a machine learning system to make a whole series of decisions from high-level synthesis down to actual low-level logic representations (…)”. According to Dean, this automated end-to-end flow could potentially reduce the time for a complex ASIC design from many months down to weeks, thus allowing the development of custom chips for a much larger range of applications.

Samsung adopts Synopsys’ machine learning-driven place-and-route solution

Major EDA vendors have already started adding machine learning capabilities to their product portfolio. Among them Synopsys, whose IC Compiler II place-and-route solution – part of the Synopsys Fusion Design Platform – includes machine learning technologies. Samsung has recently adopted Synopsys’ IC Compiler II place-and-route solution for its 5nm mobile system-on-chip production design, reporting – thanks to machine learning – up to five percent higher frequency, five percent lower leakage power and faster turn-around-time.

And Samsung’s Joydip Das, Senior Engineer at the company’s Austin R&D center, is chairing the new special interest group launched by Silicon Integration Initiative (Si2) to focus on the growing needs and opportunities in artificial intelligence and machine learning for electronic design automation. Other Si2 members participating in the SIG include Advanced Micro Devices, Ansys, Cadence, Hewlett Packard Enterprise, IBM, Intel, Intento Design, NC State University, PDF Solutions, Sandia Labs, Synopsys and the University of California, Berkeley.

Ceva unveils a superfast DSP

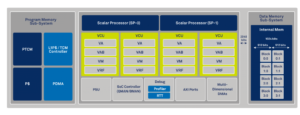

Ceva has recently announced what it claims to be “the world’s most powerful DSP architecture”, the Gen4 CEVA-XC, targeted at the most complex parallel processing workloads required for 5G endpoints and Radio Access Networks, enterprise access points and other multigigabit low latency applications. As stated in a company’s press release, the Gen4 CEVA-XC unifies the principles of scalar and vector processing enabling two-times 8-way VLIW and up to 14,000 bits of data level parallelism. The devices incorporate a pipeline architecture enabling operating speeds of 1.8 GHz at a 7nm process node using a unique physical design architecture for a fully synthesizable design flow, and an innovative multithreading design. This allows the processors to be dynamically reconfigured as either a wide SIMD machine or divided into smaller simultaneous SIMD threads. The first processor based on the Gen4 CEVA-XC architecture is the multicore CEVA-XC16, described by the company as “the fastest DSP ever made”. Architected with the latest 3GPP release specifications in mind, the CEVA-XC16 offers up to 1,600 Giga Operations Per Second that can be reconfigured as two separate parallel threads. According to Ceva, new concepts used in this device boost the performance per square millimeter when massive numbers of users are connected in a crowded area, leading to 35% die area savings for a large cluster of cores, as is typical for custom 5G base station silicon.

Ansys results

Ansys has recently reported fourth quarter 2019 GAAP and non-GAAP revenue growth of 17% and 18%, respectively, or 18% for each in constant currency. For fiscal year 2019, GAAP and non-GAAP revenue growth was 17%, or 19% in constant currency. In a press release, Ansys President & CEO Ajei Gopal stated that in 2019 the company extended its market and technology leadership and differentiated its multiphysics product portfolio both organically, as well as through strategic acquisitions, and expanded its partner ecosystem. “Our vision of making simulation pervasive across the product lifecycle is resonating with customers and partners”, he said.

Ansys has also expanded its product portfolio with the recent release of RaptorH, targeted at accelerating and improving 5G, three-dimensional integrated circuit and radio-frequency integrated circuit design workflows. RaptorH fuses features from two preexisting Ansys products: HFSS and RaptorX.

Recent acquisitions

UK-based Dialog Semiconductor – a provider of power management, charging, AC/DC power conversion, Wi-Fi and Bluetooth low energy technology – has announced the acquisition of Adesto Technologies. Based in Santa Clara, CA, Adesto is a provider of custom integrated circuits and embedded systems for the Industrial Internet of Things market. Mellanox Technologies, a supplier of interconnect solutions for data center servers and storage systems, has announced that it will acquire Titan IC, a developer of network intelligence and security technology. STMicroelectronics has signed an agreement to acquire a majority stake in Gallium Nitride specialist Exagan. Founded in 2014 and headquartered in Grenoble, France, Exagan is dedicated to accelerating the power-electronics industry’s transition from silicon-based technology to GaN-on-silicon technology, enabling smaller and more efficient electrical converters.