EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. A wafer-scale AI engine; the largest capacity FPGA; AMD’s new server processors; and more news from the industryAugust 23rd, 2019 by Roberto Frazzoli

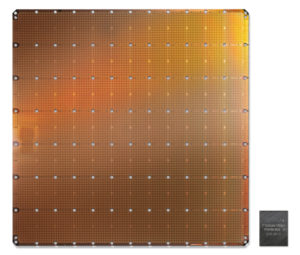

Processing hardware took center stage in August, with a number of announcements regarding AI chips, FPGAs, server processors, open source ISAs. As for the electronics industry in general, acquisition deals – one of them still in the making – attracted attention too. The 1.2 trillion transistors chip With more than 1.2 trillion transistors and an area of 46,225 square millimeters (8.5 x 8.5 inches), the Wafer Scale Engine (WSE) designed by Cerebras (Los Altos, CA) and manufactured by TSMC in its 16nm process technology is definitely an outstanding engineering achievement. Introduced at the Hot Chips conference – which took place at Stanford University from August 18 to 20 – the WSE is an Artificial Intelligence processor, aiming to compete against the GPUs commonly used for this type of applications. As Cerebras explained in a press release, it offers “400,000 AI-optimized, no-cache, no-overhead, compute cores and 18 gigabytes of local, distributed, superfast SRAM memory as the one and only level of the memory hierarchy. Memory bandwidth is 9 petabytes per second. The cores are linked together with a fine-grained, all-hardware, on-chip mesh-connected communication network that delivers an aggregate bandwidth of 100 petabits per second.” According to Cerebras, chip size is profoundly important to reduce training time and power in AI. A large silicon area provides more cores to do calculations, more memory closer to the cores, and the possibility to keep all communication on-silicon. One of the features specifically optimized for AI applications is the ‘sparsity harvesting technology’ invented by Cerebras, to boost performance on workloads that contain zeros. As the company explained, “Zeros are prevalent in deep learning calculations: often, the majority of the elements in the vectors and matrices that are to be multiplied together are zero. And yet multiplying by zero is a waste of silicon, power, and time (…). Because graphics processing units and tensor processing units are dense execution engines—engines designed to never encounter a zero—they multiply every element even when it is zero. When 50 to 98 percent of the data are zeros, as is often the case in deep learning, most of the multiplications are wasted.” Besides its significance from the AI point of view, the mega-chip is obviously interesting from a nanoelectronics technology standpoint: “The Cerebras WSE contains fundamental innovations that advance the state-of-the-art by solving decades-old technical challenges that limited chip size—such as cross-reticle connectivity, yield, power delivery, and packaging,” said Andrew Feldman, founder and CEO of Cerebras Systems.

The world’s largest capacity FPGA In terms of sheer transistor count, the Cerebras mega-chip dwarfed any other announcements this month, but still a 35 billion transistors FPGA is a significant milestone. With 9 million system logic cells, the new Virtex UltraScale+ VU19P from Xilinx is currently the world’s largest capacity FPGA. Built in a 16nm process, it features, up to 1.5 terabits per second of DDR4 memory bandwidth, up to 4.5 terabits per second of transceiver bandwidth, and over 2,000 user I/Os. TheVU19P will be generally available in the fall of 2020. New AMD server processors get positive reviews AMD has recently introduced the second generation Epyc family of processors for enterprise, cloud and high-performance computing applications. The chips feature up to 64 “Zen 2” cores in 7nm process technology. Compared to the previous generation, the new Epyc processors deliver up to 23% more instructions per clock (IPC) per core on server workloads and up to 4X more L3 Cache. Based on the AMD Infinity Architecture, the family offers improvements on I/O and memory bandwidth, including PCIe Generation 4. Google and Twitter have already announced deployments, while new platforms based on the second generation Epyc are immediately available from HPE and Lenovo. According to microprocessor analyst Linley Gwennap, “AMD's second-generation Epyc processors beat Intel's Xeon processors in several regards”. Gwennap noted that “the new design is the first server chip built in 7nm technology; although Intel's 10nm process is roughly equivalent to the TSMC 7nm node, the Xeon line will remain in 14nm for at least a year”. He also stressed that the new AMD chip is “the first server processor with PCI Express Gen4, a technology Intel plans to roll out next year in Cooper Lake. Most important – Gwennap continued – the company posted more than 80 benchmark results that show [second generation Epyc] outperforming Intel's entire Cascade Lake lineup, including the bleeding-edge 56-core model.” IBM to contribute Power ISA to the open community On August 21st, IBM announced at The Linux Foundation Open Source Summit that it will be contributing implementation rights to the Power ISA, as well as a softcore implementation of the same, and reference designs for the Open Coherent Accelerator Processor Interface (OpenCAPI) and the Open Memory Interface (OMI). IBM also announced that the OpenPower organization will move under the Linux Foundation. “With our recent Red Hat acquisition and [this] announcement, IBM becomes the only processor vendor and Power becomes the only commercially-available architecture with a completely open system stack, from the foundation of the hardware through the software stack,” said IBM's OpenPower General Manager Ken King in a press release. Acquisitions: Broadcom-Symantec, Synopsys-QTronic, ams-Osram On August 8, Broadcom announced an agreement to acquire the enterprise security business of Symantec for $10.7 billion in cash. The move is part of Broadcom's growth strategy in the infrastructure technology space, and follows the acquisitions of Brocade and CA Technologies. On August 9th, Synopsys announced an agreement to acquire Germany-based QTronic, a leader in simulation, test tools, and services for automotive software and systems development. And Austrian sensor maker ams will shortly launch a takeover offer for German photonics player Osram. The asm bid will compete against another offer; shareholders will be allowed to choose between the two. Osram has stressed that it would continue to operate under its current name, and has observed that “the integration of an industrial group with revenues of almost EUR 4 billion and a presence in some 70 countries by a significantly smaller company represents a challenging task.” |

|

|

|||||

|

|

|||||

|

|||||