Silicon Assurance, one of the ESD Alliance’s newest members, is a startup founded in 2021 to address security assurance and trust issues in silicon chips, as data breaches drive the need for better cybersecurity.

I recently spoke with Dr. Raj Gautam Dutta, co-founder and CEO of Silicon Assurance, to learn more about the challenge of building trust in silicon chips using the zero-trust security strategy model. A condensed version of our conversation is below.

Smith: What encouraged you to do an EDA startup?

Dutta: The plan to start the company was organic. A series of events unfolded in late 2018 and 2019 in the semiconductor industry including the discovery of the Spectre and Meltdown processor security flaws. That led us to believe it was the right time to open a company around the technologies we developed in our research labs at the University of Florida and the University of Central Florida.

In 2019, we saw increasing interest in our hardware security technologies from commercial semiconductor and EDA companies and had already licensed some of our technologies to these companies through the university. At that moment, we saw the need and opportunity to incorporate our technology into an EDA software package We had always envisioned taking our technologies from the lab to market and forming Silicon Assurance gave us the right platform to fulfill this objective.

Smith: What obstacles did you encounter?

Dutta: Since founding the company in 2020, we have faced many challenges. As all the founders are from academia with minimal industry experience, we have been navigating and carving out our path in this entrepreneurial world. Every step in developing the business has been a learning experience. We must also constantly remind ourselves of the difference between academic and business-oriented approaches/processes to EDA tool development. The company’s geographical location also created issues in terms of getting the attention of investors, potential customers, and employees.

The virtual communication landscape during COVID partially alleviated this challenge. We were able to conduct customer interviews and demo our software virtually. Hardware security technologies are new in the semiconductor space, and there have been many initiatives to raise awareness. However, the industry’s usage of such technologies has been slow presenting us with the challenge of driving a faster adoption rate.

Smith: Silicon Assurance focuses on chip security at the hardware level. Can you comment on the magnitude of the problem? What is the current state of chip hardware security?

Dutta: In 2019, Forrester Consulting surveyed companies with more than 500 employees for Dell Technologies. The survey showed that 63% of organizations experienced at least one data breach due to a hardware security vulnerability. The survey concluded that chip manufacturer validation and supply chain validation are critical to addressing hardware-level threats.

Subsequently, governments and the automotive industry want chips and electronic systems secure by design. In turn, the chip companies are demanding design tools that help them meet those requirements.

One way to quantify the magnitude of the problem is to look at the demand for tools for hardware security. As market data on hardware security tools are unavailable, we estimate that the total size of the hardware security tools market was over $130 million in 2021, and it is rapidly growing.

Smith: How do you define zero trust, and how is it different from “trust but verify?”

Dutta: Securing silicon chips and their supporting supply chains is crucial to prevent risks that threaten national security, global commerce and the continuity of our daily lives. Ensuring that the components and systems will behave as intended, free of defects and vulnerabilities, over their lifetime is essential to guarantee trust. Assurance strategies are a set of actions, evidence, and risk mitigation processes to ensure and demonstrate trust in a system to perform its mission.

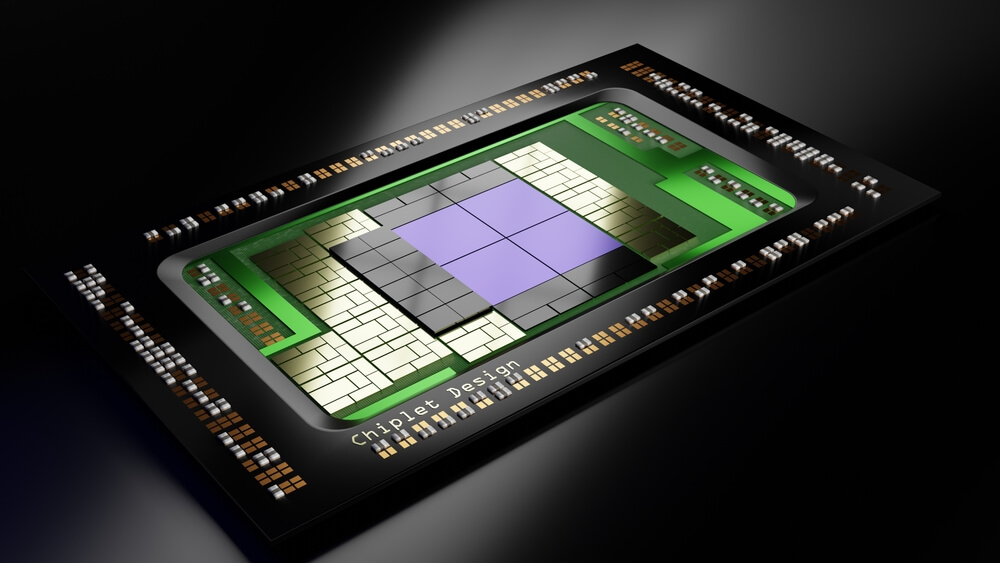

One such strategy for delivering trust in chips is “Zero Trust.” In contrast to “trust but verify,” zero trust requires that no implicit trust be put in any one system component for example a specific device, chip or SoC. Trust should be built through continual fine-grained monitoring and authentication of the quantified risk before integrating the components (chips) into the larger system (SoC).

Smith: What trends do you expect to see in 2023?

Dutta: In 2023, we will continue to see the demand for hardware security solutions increasing. The market for devices that secure sensitive data, such as hardware security modules (HSM), is projected to grow from $1.1 billion in 2022 to $2.0 billion in 2027. The key factors contributing to the growth of HSM include the requirement for effective management of cryptographic keys and adhering to strict data security compliances. Today, there are more devices, data, security breaches, and regulations in the threat landscape. Consequently, we will see more industry sectors adopting such technologies rapidly.

Another trend we anticipate seeing in 2023 will be technologies that secure the semiconductor supply chain and chips. One of the objectives of the CHIPS Act of 2022 is to protect semiconductors from sabotage in the manufacturing process. There will be demand for technologies that protect chips at the design stage and track them throughout the manufacturing, assembly, testing, and packaging stages.

Learn more about Silicon Assurance at: https://siliconassurance.com/

About Raj Gautam Dutta

About Raj Gautam Dutta

Dr. Raj Gautam Dutta is the co-founder and CEO of Silicon Assurance where his responsibilities include overlooking the technology development process, identifying business opportunities, and strategic positioning. He has been developing hardware security solutions for mor than eight years, and his research work has been published in prestigious journals and conferences. Dr. Dutta has over eight years of experience in technology transfer and technology analysis.

About the ESD Alliance

The ESD Alliance is a SEMI Technology Community representing members in the electronic system and semiconductor design ecosystem that addresses technical, marketing, economic and legislative issues affecting the entire industry. We act as the central voice to communicate and promote the value of the semiconductor design ecosystem as a vital component of the global electronics industry.

Follow SEMI ESD Alliance

www.esd-alliance.org

ESD Alliance Bridging the Frontier blog

Twitter: @ESDAlliance

LinkedIn

Facebook