Archive for the ‘Uncategorized’ Category

Tuesday, April 19th, 2022

A reminder that our first in-person CEO Outlook in three years is next week and you’re invited.

We’re expecting plenty of networking, good cheer, delicious food and, of course, questions for our panelists: Anirudh Devgan of Cadence Design Systems, Niels Fache from Keysight Technologies, Aki Fujimura of D2S, Siemens EDA’s Joe Sawicki and Simon Segars of Arm. Ed Sperling, editor in chief of Semiconductor Engineering, moderates what will be an insightful discussion.

The in-person event, co-sponsored by Keysight, will be held Thursday, April 28, at Agilent’s Building 5 at 5301 Stevens Creek Blvd. in Santa Clara, Calif., beginning at 5:30 p.m. with networking, food and beverages. The hour-long panel starts at 6:30 p.m. and is free for ESD Alliance and SEMI members. Pricing for non-members is $49 per person. More details and registration can be found at: https://bit.ly/3M728BA

Of course, this is a great opportunity to get to know the ESD Alliance, our members and our ongoing series of networking and educational events, programs and initiatives. Our Annual Membership meeting for members will be held prior to the start of the CEO Outlook beginning at 5 p.m. Non-members are welcome to attend if they purchase a ticket for the CEO Outlook.

Contact me at bsmith@semi.org if you have questions or need more information. Or, seek me out at next week’s CEO Outlook.

Engage with the ESD Alliance at:

Website: www.esd-alliance.org

ESD Alliance Bridging the Frontier blog

Twitter: @ESDAlliance

LinkedIn

Facebook

No Comments »

Tuesday, April 5th, 2022

Here’s some great news for members of the electronic system design community! Our part of the semiconductor industry continued to report double-digit year-over-year revenue growth for Q4 2021 and ended 2021 with $13.2 billion total market revenue, based on our latest Electronic Design Market Data (EDMD) report.

Revenue increased 14.4% from $3,031.5 million in Q4 2020 to $3,468.2 million in Q4 2021.The four-quarter moving average comparing the most recent four quarters to the prior four rose 15.8 %. “Computer-Aided Engineering, Printed Circuit Board and Multi-Chip Module, Semiconductor Intellectual Property categories, and Services recorded double-digit growth for the quarter,” remarked Wally Rhines, Executive Sponsor of the SEMI EDMD report, in announcing the results. “Geographically, the Americas, EMEA and AsiaPac all reported revenue growth.”

(more…)

No Comments »

Wednesday, March 30th, 2022

It’s going to be a busy and exciting few weeks for the Electronic System Design Alliance (ESD Alliance) and our community at large. Perhaps you might like to join us for our two in-person events.

CEO Outlook

We start with the return of our CEO Outlook Thursday, April 28, in Santa Clara, Calif., with Ed Sperling, editor in chief of Semiconductor Engineering, serving as moderator. Joining him as panelists are Dr. Anirudh Devgan of Cadence Design Systems, Niels Fache from Keysight Technologies, Aki Fujimura of D2S, Siemens EDA’s Joe Sawicki and Simon Segars of Arm.

The in-person event, co-sponsored by Keysight, will be held at Agilent’s Building 5 at 5301 Stevens Creek Blvd. in Santa Clara, Calif., beginning at 5:30pm PDT with a networking reception with food and beverages. The CEO Outlook discussion begins at 6:30pm. It is free for ESD Alliance and SEMI members. Pricing for non-members is $49 per person. Click here for registration information.

The ESD Alliance Annual Membership meeting will be held prior to the start of the CEO Outlook beginning at 5pm. Non-members are welcome to attend if they purchase a ticket for the CEO Outlook.

(more…)

No Comments »

Thursday, March 24th, 2022

Verific is a well-known name within the electronic system design community. Not long ago, its president and COO Michiel Ligthart and I talked about trends in chip design for a post on the SEMI website. It’s posted below in its entirety.

And, a reminder to join us for our CEO Outlook as it returns in-person Thursday, April 28. The hour-long panel starts at 6:30 p.m. and is free for ESD Alliance and SEMI members. Pricing for non-members is $49 per person. Registration: https://bit.ly/3D7QW4a

Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification.

(more…)

No Comments »

Thursday, March 17th, 2022

Great news for the electronic system design community –– the ESD Alliance CEO Outlook returns Thursday, April 28, in-person in Santa Clara, Calif. Reprising his role as moderator is Ed Sperling, editor in chief of Semiconductor Engineering. Joining him as panelists are Anirudh Devgan of Cadence Design Systems, Niels Fache from Keysight Technologies, Aki Fujimura of D2S, Siemens EDA’s Joe Sawicki and Simon Segars of Arm. Great news for the electronic system design community –– the ESD Alliance CEO Outlook returns Thursday, April 28, in-person in Santa Clara, Calif. Reprising his role as moderator is Ed Sperling, editor in chief of Semiconductor Engineering. Joining him as panelists are Anirudh Devgan of Cadence Design Systems, Niels Fache from Keysight Technologies, Aki Fujimura of D2S, Siemens EDA’s Joe Sawicki and Simon Segars of Arm.

The event, co-sponsored by Keysight, will be held at Agilent’s Building 5 at 5301 Stevens Creek Blvd. in Santa Clara, Calif., beginning at 5:30 p.m. P.D.T with networking, food and beverages. The hour-long panel starts at 6:30 p.m. and is free for ESD Alliance and SEMI members. Pricing for non-members is $49 per person. Click here for registration information.

The ESD Alliance Annual Membership meeting for members will be held prior to the start of the CEO Outlook beginning at 5 p.m. Non-members are welcome to attend if they purchase a ticket for the CEO Outlook.

I’m also pleased to announce a new member of the ESD Alliance, a SEMI Technology Community. Xpeedic of Shanghai, China, and Bellevue, Wash., is noted for addressing challenges across the full spectrum of chip, package and system designs with an EDA simulation platform supporting advanced nodes and packaging to enable next-generation high-frequency, high-speed integrated systems. Its products are powered by its proprietary electromagnetic and circuit solver technologies. I’m also pleased to announce a new member of the ESD Alliance, a SEMI Technology Community. Xpeedic of Shanghai, China, and Bellevue, Wash., is noted for addressing challenges across the full spectrum of chip, package and system designs with an EDA simulation platform supporting advanced nodes and packaging to enable next-generation high-frequency, high-speed integrated systems. Its products are powered by its proprietary electromagnetic and circuit solver technologies.

Dr. Feng Ling, Xpeedic’s CEO, noted: “The ESD Alliance is a great platform to promote the EDA industry because it plays an invaluable role in bringing new technologies and new products into the market. Being an ESD Alliance member, we hope to increase the visibility of our technologies and products throughout the semiconductor design ecosystem.”

(more…)

No Comments »

Thursday, March 3rd, 2022

I’m pleased to welcome Excellicon as a new member of the Electronic System Design Alliance and know it will benefit from our varied initiatives, networking opportunities and brand exposure through SEMI’s global presence. I’m pleased to welcome Excellicon as a new member of the Electronic System Design Alliance and know it will benefit from our varied initiatives, networking opportunities and brand exposure through SEMI’s global presence.

Himanshu Bhatnagar, Excellicon’s CEO, agrees. “It’s clear that the ESD Alliance is the hub of the electronic system design ecosystem and important for us to be actively involved. Our technology has been customer proven and we are looking forward to expanding our brand awareness via our membership in the SEMI ESD Alliance.” As a member of the ESD Alliance, Excellicon is also a member of SEMI, the global industry association representing the worldwide electronic product design and manufacturing supply chain.Excellicon hails from Laguna Hills, Calif., and provides EDA software for timing constraints authoring, compiling, verification, formal validation and management using a multi-mode approach. It has capabilities for verification of floor plans and offers the ability to assess viability of various floor plans scenarios and perform what-if analyses.

Welcome Excellicon!

(more…)

No Comments »

Tuesday, February 15th, 2022

Nikos Zervas, CAST’s CEO, and I discuss the early days of the IP business in a post that originally appeared on the SEMI website in October as part of my SEMI blog post series.

In the early 1990s, engineers of varying degrees of skill with a powerful PC set up shop designing and selling blocks or libraries of reusable components with a defined interface and behavior. These blocks, known as intellectual property, or IP, were then (and still are) integrated into a larger design. In the early 1990s, engineers of varying degrees of skill with a powerful PC set up shop designing and selling blocks or libraries of reusable components with a defined interface and behavior. These blocks, known as intellectual property, or IP, were then (and still are) integrated into a larger design.

While the new market segment created excitement and new opportunities, it also was untested and created uncertainty. Many fledgling companies failed. It’s a different story today. Arm, as well as Cadence and Synopsys, are silicon IP suppliers and the segment’s yearly revenue tops $4 billion, a long way from those early garage startup days.

ESD Alliance member CAST, a silicon IP provider since 1993, participated in the remarkable growth and impact on the semiconductor industry. Nikos Zervas, CAST’s CEO, and I discuss those early days of the IP business and what’s ahead.

(more…)

No Comments »

Tuesday, January 25th, 2022

In my recurring blog post series for SEMI, I interviewed Michiel Ligthart, president and COO. Here’s the Q&A as it appeared on the SEMI website in October.

Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification. Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification.

I spoke with Verific president and COO Michiel Ligthart about homegrown and open-source EDA tools and other recent trends in chip design.

Smith: What trends are you seeing in chip design?

Ligthart: Semiconductor companies are starting to build a portfolio of intellectual property, including homegrown electronic design automation (EDA) tools, that they want to keep secure and differentiated from their competitors. The increased interest in internally developed and supported EDA tools is a trend we started to see about two years ago. It’s not simulation, synthesis or place and route (P&R). Instead, it’s pieces of a chip design flow optimized for a company’s specific needs.

In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example. In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.

Is this a widespread trend? It could be. We hear about it within end-user applications ranging from 5G and AI to data center processors and there are probably others we don’t hear about. Power optimization is an example of the kind of specific internal need being addressed.

(more…)

No Comments »

Sunday, January 16th, 2022

Let’s cheer for a piece of great news –– the Electronic System Design industry revenue increased 17.1% year-over-year from $2,953.9 million to $3,458.1 million in Q3 2021! This comes from the most recent Electronic Design Market Data (EDMD) report produced by the ESD Alliance, a SEMI Technology Community, where I serve as Executive Director.

The four-quarter moving average comparing the most recent four quarters to the prior four rose 16.1%. All regions reported double-digit growth with product categories CAE, Printed Circuit Board and Multi-Chip Module, semiconductor IP and Services showing double-digit growth.

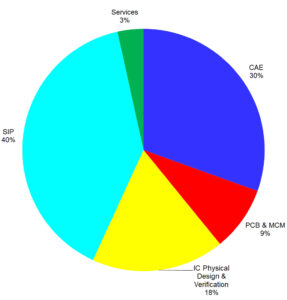

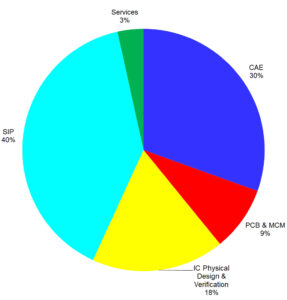

Q3 2021 revenue percentage by category Taking a deeper dive into the year-over-year revenue by product and application category shows:

- CAE revenue increased 13.7% to $1,054.7 million and the four-quarter moving average increased 11.8%.

- IC Physical Design and Verification revenue rose 0.7% to $612.6 million with the four-quarter moving average of 16% growth.

- Printed Circuit Board and Multi-Chip Module (PCB and MCM) revenue increased 14.5% to $298.3 million. The four-quarter moving average saw an increase of 10.9%.

- Semiconductor IP revenue rose 30.6% to $1,373.3 million for a four-quarter moving average of 22.1% growth.

- Services revenue increased 12.5% to $119.1 million. The four-quarter moving average increased 9.2%.

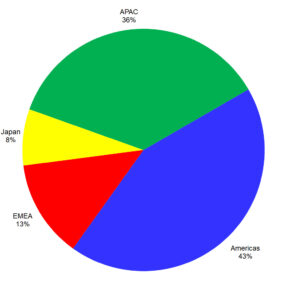

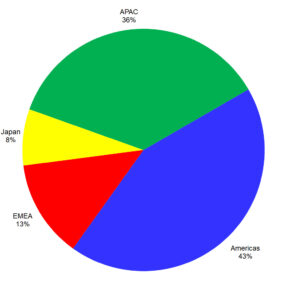

Q3 20201 revenue percentage by region As for the year-over-year revenue change by region:

- The largest reporting region by revenue is the Americas. The region purchased $1,494.5 million of ESD products and services in Q3 2021, a 14.3% increase. The four-quarter moving average rose 15.8%.

- Europe, Middle East, and Africa (EMEA) revenue increased 22.6% to $451.7 million with a four-quarter moving average of 11.9% growth.

- Japan revenue increased 11.8% to $259.8 million and the four-quarter moving average rose 3.3%.

- Asia Pacific (APAC) revenue increased 19.7% to $1,252.1 million. The four-quarter moving average grew by 21.3%.

Significantly, companies tracked in the EDMD report employed 51,182 people globally in Q3 2021, an 8.7% increase over the Q3 2020 headcount of 47,087 and up 2.4% compared to Q2 2021.

The ESD Alliance Electronic Design Market Data (EDMD), formerly known as the Market Statistics Service, report has much more detailed information than provided here. Published quarterly, it presents EDA, SIP and services industry revenue data from public and private companies. Each quarterly report is published approximately three months after quarter close.

(more…)

No Comments »

Monday, January 10th, 2022

I originally wrote an article drawing comparisons between chip design and manufacturing and winemaking back in 2009. While a lot has changed since then, especially in the semiconductor and electronics industry, many of the comparisons still hold true. I originally wrote an article drawing comparisons between chip design and manufacturing and winemaking back in 2009. While a lot has changed since then, especially in the semiconductor and electronics industry, many of the comparisons still hold true.

From a high-level view, what do chip design and manufacturing have in common with winemaking?

It turns out that, in both cases, it’s all about the process. Although I have spent much of my career in the semiconductor, EDA and IP industries, I have had the opportunity to participate in a small, commercial winemaking venture called Jazz Cellars for the past 16 years. It might sound like a stretch (so bear with me) but I think there are some interesting parallels and a few significant differences between the processes involved in producing wine and semiconductor chips.

One shared characteristic of both chip design and winemaking is that there is no instant gratification –– it takes time and effort to yield a great end product. While it may be possible to turnaround a simple chip design in a few months, most complex designs often take years to go from concept to market. The same is true for a wine –– many red wines are not released until three or more years after the grapes were initially harvested. There are exceptions of course such as Beaujolais Nouveau, always released on the third Thursday of November, and some white wines that may be released just a few months after they are harvested. One shared characteristic of both chip design and winemaking is that there is no instant gratification –– it takes time and effort to yield a great end product. While it may be possible to turnaround a simple chip design in a few months, most complex designs often take years to go from concept to market. The same is true for a wine –– many red wines are not released until three or more years after the grapes were initially harvested. There are exceptions of course such as Beaujolais Nouveau, always released on the third Thursday of November, and some white wines that may be released just a few months after they are harvested.

Let’s look at some of the similarities between the processes involved in winemaking and chip design. For the sake of discussion, I am assuming a generalized, high-level description of the processes involved.

Both processes start with an initial plan. For the chip, the plan is the system design and global specifications for the chip –– its functional spec, operating speed, power consumption, target process technology, interface, package type, and the like. In winemaking, the plan describes what type of finished wine we are trying to achieve. This includes the varietal of grape and the profile of the finished wine. For example, we may decide to make an aggressive red wine with a strong tannin profile that will age for a long time or we may decide that we want to make a soft, fruit-forward wine that will be easily drinkable early on.

(more…)

No Comments »

|

In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.

In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.