Posts Tagged ‘UVM’

Thursday, September 23rd, 2021

As regular readers know, Agnisys is the leader in specification automation. From various forms of executable design specifications, we generate the SystemVerilog RTL design, Universal Verification Methodology (UVM) testbench models for simulation, assertions for formal analysis, C/C++ code for embedded processors, sequences for both UVM and C/C++, and user documentation. The designers incorporate the RTL code into their chip, the verification engineers use the UVM models, sequences, and assertions to verify the RTL design, and the embedded programming team uses the C/C++ code as a starting point for their firmware and drivers.

Eventually, the system must be validated with the hardware and production software running together. Ideally, this happens using an emulator or an FPGA prototype before tapeout, so that no surprises are found when the software runs on the fabricated chip in the bring-up lab. However, there is a step in between hardware verification and system validation, often called system-level verification or early validation, that’s essential for complex system-on-chip (SoC) designs. At this stage, the verification team runs both a UVM testbench and embedded C/C++ test code together in simulation.

(more…)

Tags: C/C++, RTL, testbench, UVM

No Comments »

Monday, July 19th, 2021

In my last post, I mentioned that Agnisys is currently in the middle of a series of new webinars on how specification automation benefits many teams developing intellectual property (IP) blocks and system-on-chip (SoC) designs. When we first started supporting register and memory automation, we focused on generating register-transfer-level (RTL) design descriptions and Universal Verification Methodology (UVM) simulation testbench models from executable specifications. You generate these outputs as soon as the specifications are ready and re-generate them every time that the specifications are updated throughout the project.

This is of clear benefit to design and verification engineers. The designers never have to write any RTL code for registers or memories, or update code manually when requirements change. Similarly, the verification team developing the UVM testbench for the IP or SoC incorporates the generated models without having to develop them by hand, and automatically updates them when needed. When we added sequence automation to our product family, we helped the UVM effort even more. Over time, we’ve added design and verification generation for a wide range of standards-based IP as well as SoC-level interconnection of IP and custom blocks.

(more…)

Tags: SemiEDA, SoC, SystemRDL, UVM

No Comments »

Thursday, March 25th, 2021

The last month has been busy for all of us at Agnisys, with three important virtual events. As I previewed in my last post, we held our first Agnisys User Group Educational Roundtable (AUGER) on March 18. We had a great event enhanced by lots of interaction with our users. Prior to that, we presented the paper “ML-Based Verification and Regression Automation” and the short workshop “RISC-V Based SoC Design, Verification and Validation in One Hour” at the annual Design and Verification Conference (DVCon) U.S. We also participated for the first time in DVClub Europe, where I discussed “Automating IP and SoC Verification.”

As part of preparing for these events, we took a step back and thought from the top down about the role we are playing in the industry today and the directions we can take in the future. We have expanded our original focus on register automation to encompass specification-driven design, verification, embedded programming, validation, and documentation of IPs and SoCs. This expansion is testament both to our growth as a company and to the many challenges faced by semiconductor development teams. Sheer complexity is the most obvious issue; today’s designs contain billions of gates with thousands of blocks and countless interconnections.

(more…)

Tags: SemiEDA, UVM

No Comments »

Tuesday, January 26th, 2021

Recently, I’ve been thinking about how vital partners are to the EDA industry in general, and for Agnisys in particular. When I thought about writing a blog post on this topic, I asked myself whether this might be of interest to anyone beyond other EDA companies. After some consideration, I realized that who we partner with, and how, and why, is quite important for our users. In fact, when I talk with both prospective and current customers, this is a topic that comes up quite often. So, I decided to give some background on the way that EDA partnerships work and cite a few noteworthy examples.

Let me start with why the idea of partnerships exists at all. The reason is simple: users demand that their EDA vendors work together. The reality is that every chip development team uses tools from multiple vendors. No single vendor, not even any of the “Big 3” industry leaders, offers every possible tool and form of IP required for a comprehensive chip design and verification flow. Users need to be able to choose best-in-class tools from different vendors and deploy them together on a single project. However, users do not want to have to integrate and test the tools together all by themselves.

(more…)

Tags: EDA, SystemVerilog, testbench, UVM

No Comments »

Friday, December 11th, 2020

When engineers discuss system-on-chip (SoC) designs, they’re almost always talking about embedded systems with both hardware and software content. In fact, many argue that a chip must contain at least one embedded processor to qualify as an SoC. Embedded systems have many design and verification challenges, and these apply fully to SoCs. The silicon technology really doesn’t matter; embedded FPGA designs can be huge these days and every bit as complex as ASICs or full-custom chips. Tackling the development challenges for these systems requires an automated, unified flow that covers both hardware and software, spanning design, verification, software, and documentation.

(more…)

Tags: Agnisys, UVM

No Comments »

Thursday, October 15th, 2020

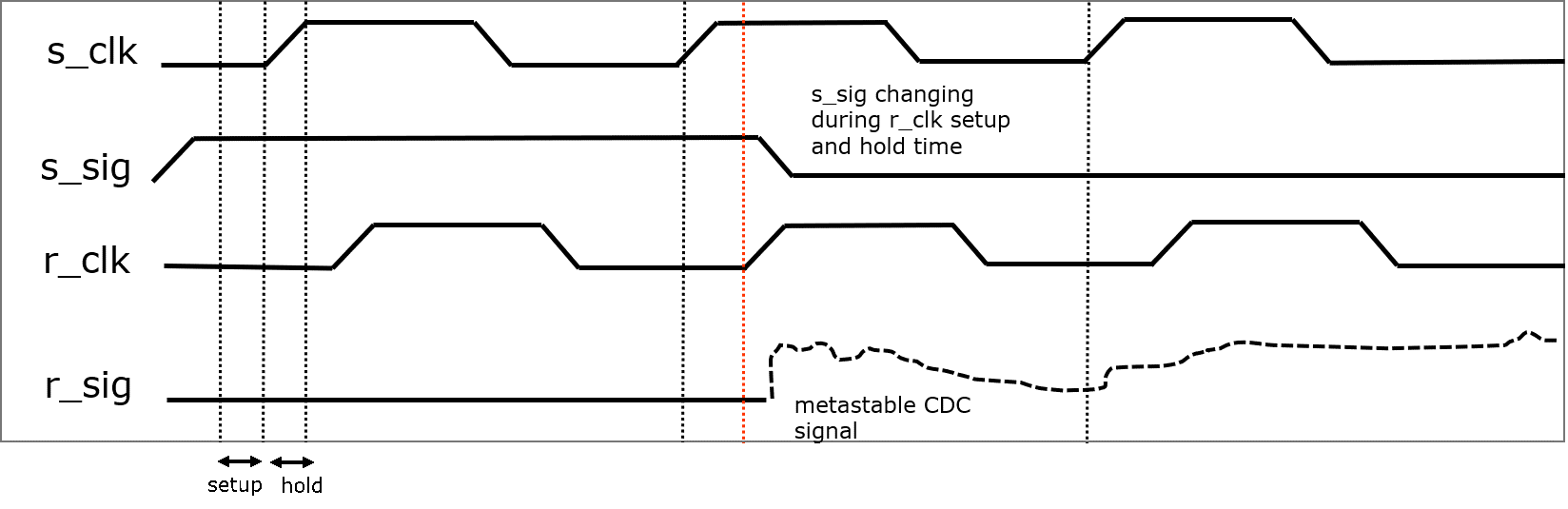

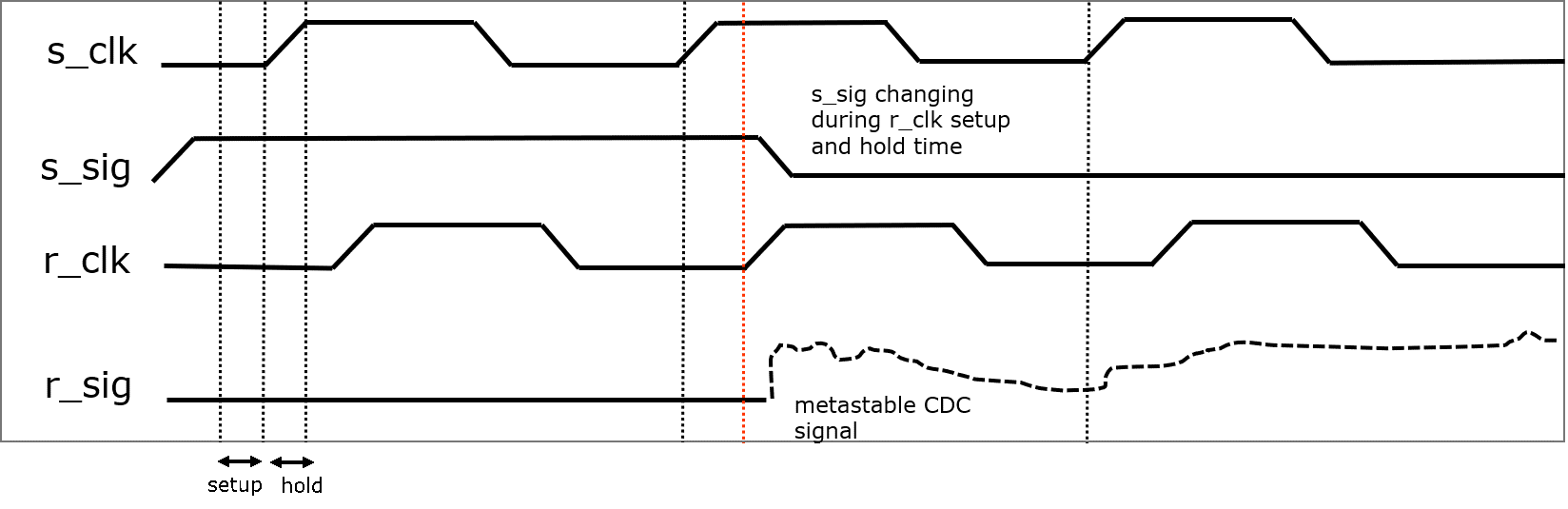

Register-transfer-level (RTL) code, formal analysis, RTL simulation, and logic synthesis have all raised the abstraction level of electronic design and verification. Today’s designers operate very differently than their predecessors who drew circuit-level schematics and ran only SPICE. However, underneath all this abstraction the physical properties of electronic devices remain unchanged, and these must be considered during design. One well-known example is metastability, which can occur wherever a signal crosses between flip-flops running on asynchronous clocks, known as a clock domain crossing (CDC).

The most common example of metastability happens when the output value of a flip-flop on the sending clock changes during the setup and hold time of the clock for the receiving flip-flop. The output of the flip-flop on the receiving clock can take on an indeterminate value that requires some time to settle to a one or zero. If the output of the receiving flip-flop is used immediately, an invalid value may be fed into the downstream logic and produce incorrect results. Unfortunately, there is no way to design a flip-flop that does not have a risk of metastability.

(more…)

Tags: sysremRDL, SystemVerilog, UVM

No Comments »

Tuesday, September 22nd, 2020

In February, we will celebrate the tenth anniversary of Accellera approving the first version of the Universal Verification Methodology (UVM). It’s no exaggeration to say that UVM changed the world of semiconductor verification. It wasn’t the first verification methodology, and not even the first to use SystemVerilog, but it was developed and supported by all major electronic design automation (EDA) vendors. Users could write testbenches using the UVM building-block library and its detailed guidelines, secure in the knowledge that simulators and other tools would handle them properly.

UVM focused the diverse set of constructs and powerful capabilities available in SystemVerilog on the specific task of building a reusable verification environment. Object-oriented programming (OOP) support meant that users could extend the building blocks without modifying them. Adherence to the guidelines made verification components reusable “horizontally” across projects and even across companies. Passive components such as monitors and coverage collectors, and even some active interface models, could be reused “vertically” from block to subsystem to system.

(more…)

Tags: testbench, UVM

No Comments »

Thursday, May 28th, 2020

A recent blog post noted that today’s RTL design verification (DV) environments are very powerful and very complex. The SystemVerilog-based Universal Verification Methodology (UVM) standard provides most of the key building blocks for the simulation testbenches at the heart of the DV process. The previous post focused on correct-by-construction of UVM testbenches using the DVinsight™ smart editor from Agnisys. This post shows how other solutions from Agnisys can automate the generation of the UVM Register Abstraction Layer (RAL) that provides testbench access to the registers and memories in the design being verified.

(more…)

Tags: IDesignSpec, IP-XACT, SystemVerilog, testbench, UVM

No Comments »

Thursday, April 23rd, 2020

Modern RTL design verification (DV) environments are both very powerful and very complex. They include advanced simulation testbenches plus support for formal verification, virtual prototypes, and emulation technology. Even within just the testbench, there is a great deal of highly sophisticated code to be written. Part of the power and complexity comes from the capabilities of the testbench. At the core is constrained-random stimulus generation, automated tests that exercise many parts of the design while staying within the rules for input sequences. Important testbench components include interfaces, register models, bus agents, reused verification IP (VIP), results checkers, and coverage monitors. Clearly, a lot of effort is needed to create and maintain this infrastructure. A typical infrastructure is shown in the following diagram:

(more…)

Tags: DVinsight, RTL design, SystemVerilog, UVM

No Comments »

Monday, February 3rd, 2020

The growth of new technologies such as artificial intelligence, machine learning, Internet of Things (IoT), virtual/augmented reality and of course, the various technologies for the automotive industry has led to a new surge in the development of semiconductor chips. The growth had been stunted in part due to the considerable cost involved in using the processor core, which forms the heart of most SoCs. The enormous cost, risk, development time and necessary volumes of developing a processor, has kept this lucrative industry in the hands of just a few companies. That is, until now.

With the development of the open source RISC-V ISA from UC Berkeley labs, based on the new computing needs in various power and performance dimensions, the semiconductor industry is once again at the cusp of embracing an incredible surge in innovation. Over the last few years, the interest in RISC-V has been gaining steam with commercial implementations and adoption growing rapidly.

(more…)

Tags: IoT, RISC, RISC-V, RTL, SoCs, UVM

No Comments »

|