Agnisys Automation Review Anupam Bakshi

Anupam Bakshi is Chief Executive Officer (CEO) for Agnisys, Inc., the pioneer and industry leader in Golden Executable Specification Solutions™. From his early days at Gateway Design Automation, through to his time at Cadence, PictureTel, and Avid Technology, he has been passionate about … More » A Quick Look Back at a Virtual DACAugust 4th, 2020 by Anupam Bakshi

In my last blog post, I talked a bit about the history of the annual Design Automation Conference (DAC) and mentioned that this year it would be a virtual event due to the ongoing pandemic. The show concluded about ten days ago and so we’ve now had time to assess the results. I thought that some of you who were unable to attend might be curious how it went, so I’d like to provide a quick summary. The first thing to say is that virtual events are still novel and a bit daunting for both exhibitors and attendees. This was the first virtual show for Agnisys, so it took some adjustment to our usual preparation and promotional efforts. The good news is that we had an impressive number of visitors to our DAC virtual booth, so lots of you were able to find out about us, our products, and our customers. We also had a quiz that proved quite popular. The less-good news is that some visitors didn’t navigate to the deeper engagement options. It seemed that the concept of the virtual booth was unclear, plus many users (including our own engineers) were stymied by technical issues on the DAC site. DAC May Be Virtual, but Our New Products Are NotJuly 18th, 2020 by Anupam Bakshi

Anyone who’s worked in the EDA industry, and many of its customers, are aware of the annual Design Automation Conference (DAC). This event dates back 57 years, a long time for anything to last in our high-tech world. It’s really two shows in one: a competitive, peer-reviewed technical conference combined with a large vendor exhibition. We have been attending DAC since 2009 and have always found it to be a valuable experience. The technical program is stimulating, we get to check out what other vendors are doing, and we’re able to talk to many customers and prospective customers over the span of just a few days. Of course, this year is different. As for most other public events and shows, it’s not possible for us to gather together physically at this time. Therefore, DAC 2020 is a virtual event, with the speakers delivering their talks and papers online and the vendors hosting virtual booths. Agnisys is participating as always and we are looking forward to engaging with all of you in a different but still personal way. The virtual booths are configured to enable real-time chats and schedule detailed discussions. We can’t meet face to face or shake hands, but we can listen to your chip design and verification challenges and suggest ways that we can help. Read the rest of DAC May Be Virtual, but Our New Products Are Not Smart Assembly of SoC DesignsJune 29th, 2020 by Anupam Bakshi

System-on-chip (SoC) projects are, by their very nature, complex and difficult to complete successfully. Specification, architecture, design, and verification are all challenging. This blog post focuses on the challenges faced by designers, driven by the convergence of applications onto a single SoC device. This increases the demand for design functionality and design performance. At the same time, market requirements generate pressure to drive down the cost of design and meet shrinking market windows due to shorter product shelf lives. Every step of the design process has become more difficult, even the seemingly simple task of assembling all the pieces that make up the SoC. Today’s large chips may contain 500 of more instances of intellectual property (IP), a combination of new designs, reused blocks from previous projects, and licensed commercial IP. If each of these blocks averages 50 ports, then 25,000 connections must be made among them. Making these connections manually is tedious and time-consuming, with a high chance of errors. Meeting cost and schedule goals requires a big increase in the productivity of the SoC design team. Methodology improvements are needed to help accelerate assembly of chips and systems through automation.

The best solution is providing designers flexible, customizable, and configurable IP and subsystem generators along with a tool to automate architectural level SoC assembly and connectivity. The capabilities for such a solution include:

Three Steps to Set Up a RISC-V SoC UVM TestbenchJune 17th, 2020 by Anupam Bakshi

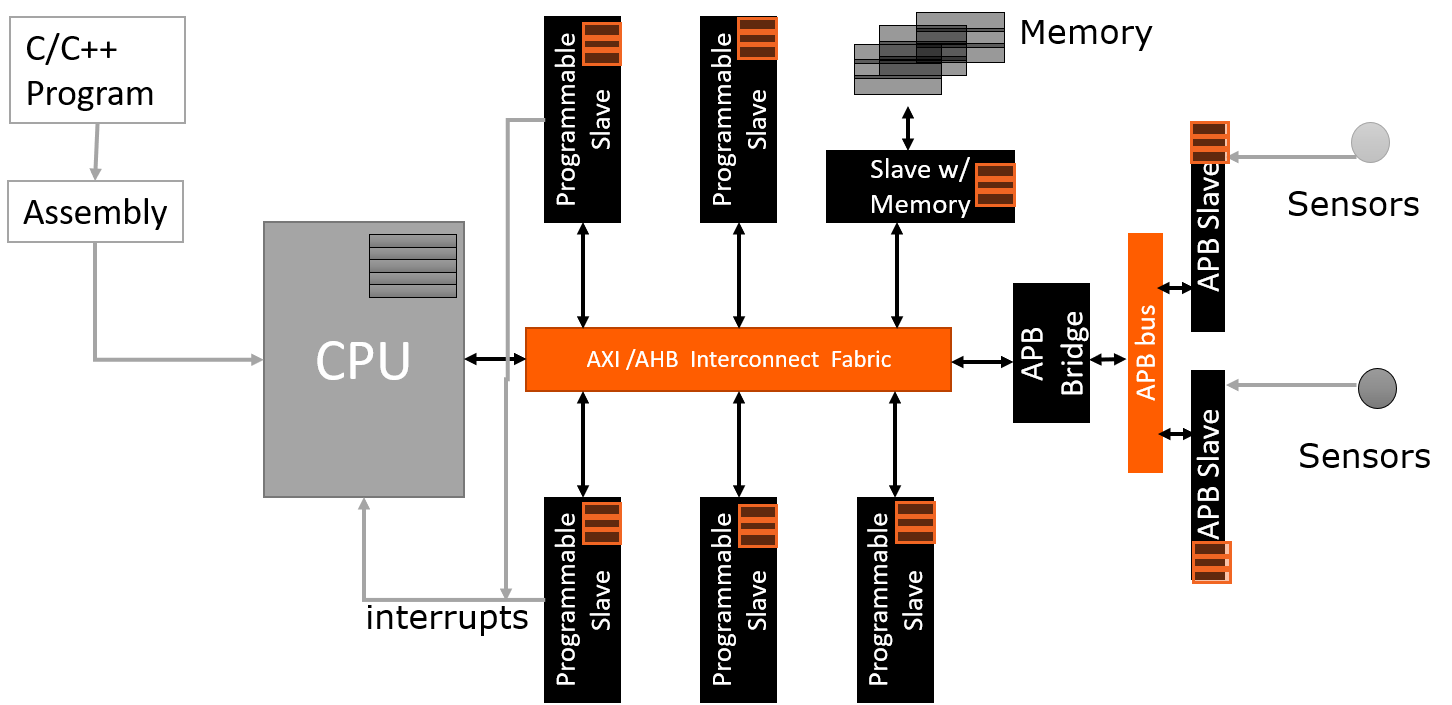

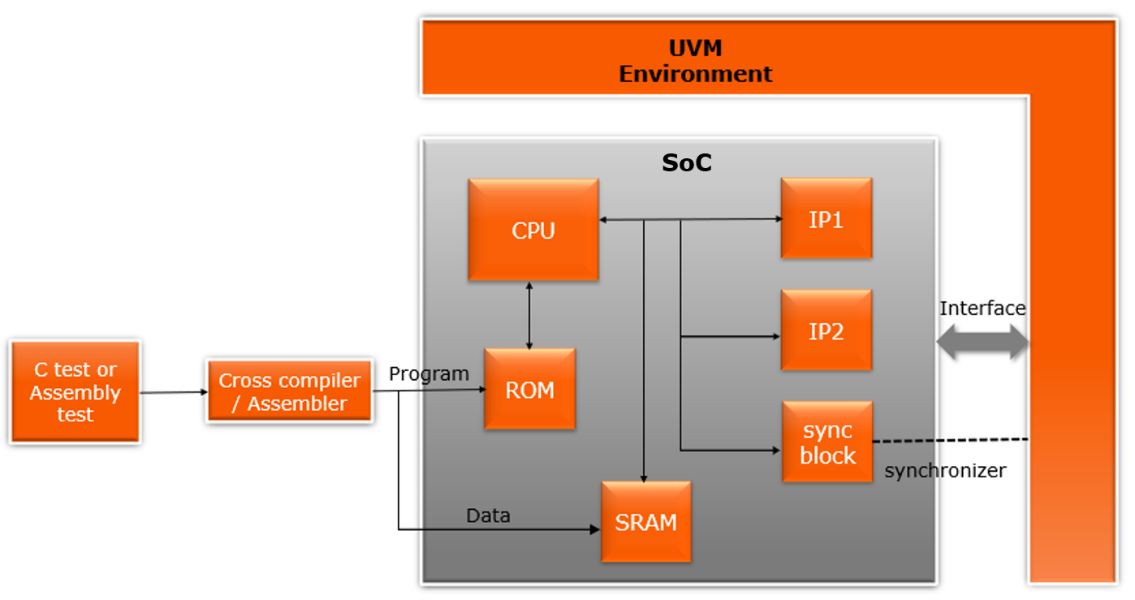

Verifying any large chip design is challenging, but a system-on-chip (SoC) presents additional requirements. By definition, an SoC includes one or more embedded processors, and the code they execute provides a significant portion of the overall functionality. Both the hardware and software must be verified, but they also must be verified together (co-verified) to exercise the full range of intended operation. Although lint checks, formal analysis, and other techniques play a role, the bulk of verification is performed by simulating a testbench compliant with the Universal Verification Methodology (UVM) standard. Such a testbench environment is a must-have requirement for every SoC project. It provides a means to check the full system before sending the design to the foundry for fabrication. It complements block-level testbenches by verifying that all the connections between the blocks are functioning correctly, that data flows properly around the SoC, and that hardware interrupts and their associated interrupt service routine (ISR) software are working. The testbench can also help the firmware and software engineers write and debug device drivers and applications. Setting up the SoC verification environment can be divided into three steps:

The process is similar for any type of embedded processor, but this post focuses on RISC-V since it is a widely used instruction set architecture (ISA) for contemporary SoCs.

Read the rest of Three Steps to Set Up a RISC-V SoC UVM Testbench Automation of the UVM Register Abstraction LayerMay 28th, 2020 by Anupam Bakshi

A recent blog post noted that today’s RTL design verification (DV) environments are very powerful and very complex. The SystemVerilog-based Universal Verification Methodology (UVM) standard provides most of the key building blocks for the simulation testbenches at the heart of the DV process. The previous post focused on correct-by-construction of UVM testbenches using the DVinsight™ smart editor from Agnisys. This post shows how other solutions from Agnisys can automate the generation of the UVM Register Abstraction Layer (RAL) that provides testbench access to the registers and memories in the design being verified. Read the rest of Automation of the UVM Register Abstraction Layer Doing What We Can in Challenging TimesMay 9th, 2020 by Anupam Bakshi

Most of us have faced difficulties in our personal and professional lives, and have worked our way through them. But few of us have experience dealing with a challenge as broad and disruptive as the COVID-19 global pandemic. By now, many people know friends and family members who have been sickened or even struck down by this disease. The economic toll is staggering, and recovery will take considerable time. Even with all the coping mechanisms we have developed through dealing with past challenges in our lives, it’s easy to feel overwhelmed. I think that the best way to handle the stress and uncertainty is to do whatever we can to help our families and community, and those everywhere suffering directly or indirectly from the virus. As an example, a diverse group of companies and institutions recently took an innovative step to establish the Open COVID Pledge. This initiative offers intellectual property (IP) free of charge for the purpose of diagnosing, preventing, containing, and treating COVID-19. Correct-By-Construction SystemVerilog UVM TestbenchesApril 23rd, 2020 by Anupam Bakshi

Modern RTL design verification (DV) environments are both very powerful and very complex. They include advanced simulation testbenches plus support for formal verification, virtual prototypes, and emulation technology. Even within just the testbench, there is a great deal of highly sophisticated code to be written. Part of the power and complexity comes from the capabilities of the testbench. At the core is constrained-random stimulus generation, automated tests that exercise many parts of the design while staying within the rules for input sequences. Important testbench components include interfaces, register models, bus agents, reused verification IP (VIP), results checkers, and coverage monitors. Clearly, a lot of effort is needed to create and maintain this infrastructure. A typical infrastructure is shown in the following diagram:

Read the rest of Correct-By-Construction SystemVerilog UVM Testbenches Enhance Your Design and Verification Knowledge with Extensive Webinar SeriesApril 8th, 2020 by Anupam Bakshi

There is no easier way to learn new material than with a webinar in the comfort of your own home or office. Webinars bring experts directly to you with the latest results from both research and practical experience. Live webinars offer immediacy and interaction, while recorded webinars offer the chance for many more participants to benefit from the material over time. At Agnisys, we have found that webinars are an excellent way to educate the industry on key design and verification challenges in IP/FPGA/ASIC development. With the current circumstances in the world and so many engineers working from home, all forms of online learning are more important than ever. Read the rest of Enhance Your Design and Verification Knowledge with Extensive Webinar Series Automating Design AssemblyMarch 3rd, 2020 by Anupam Bakshi

The consumer revolution over the past few decades has funneled a growth of SoC chips primarily in the area of consumer electronics. This revolution along with the increase of automotive and industrial electronics has led to a trend in convergence of applications on a single device. Companies vying for a bigger share of the market place are enticing their consumers by offering new or better features, which often adds to design complexities. In this competitive food chain, chip design companies are tragetting the companies developing these consumer devices with a range of functionalities embedded in single chip solutions. This convergence in applications as well as the growth of new technologies such as IoT, augmented reality, AI etc. has resulted in increasing demands on design complexity and design performance. With an increase in design complexity and a reduction in time to market, chip designers are now grappling with ways to meet the performance requirements while at the same time reduce the design cycle. Consequently, design teams are increasingly compelled to look at methodology changes that can help accelerate chip assembly through one or multiple forms of automation. From specifying registers in SystemRDL to implementing the test intent using PSSFebruary 21st, 2020 by Anupam Bakshi

The complex SoCs of today typically contain thousands of registers, which are used to control the operations of the SoC/IP. The register specification, which is at the epicenter of a SoC/IP design is accessed by different teams such as hardware, software, verification and embedded design teams, all of which need to access the same source. A mismatch and misinterpretation of the specification simply results in un-necessary delays to the development cycle. While there are several methods to define the register specification, such as Excel, Word, IP-XACT etc., SystemRDL is gaining popularity, as it is an easy-to-use textual language used for the design and delivery of SoCs/IPs. Released by Accellera, SystemRDL supports the complete project cycle of registers from the specification, model generation, and design verification to maintenance and documentation. It mitigates the problems encountered in describing and managing registers. SystemRDL enables a system architect or a hardware designer to create a functional specification of the hardware-software interface (HSI) for an SoC/IP, which can include addressable registers, interrupts, counters etc. This specification is then used by other members of the team including software, hardware and design verification to create representations of data in the languages they use in their aspect of the SoC development process. Read the rest of From specifying registers in SystemRDL to implementing the test intent using PSS |

|

|

|||||

|

|

|||||

|

|||||