Siemens EDA Romain Petit

Romain Petit joined Siemens in 2014 as an associate application engineer, working on hardware emulation. He is now the product marketing manager for the Siemens proFPGA CS software prototyping platform. Multi-FPGA Partitioning – What’s the Recipe for Success?November 12th, 2024 by Romain Petit

Multi-FPGA partitioning has undergone significant advancements over the years, driven by the increasing complexity of digital systems and the need for efficient prototyping and verification. Today’s prototypes require dozens of the larger FPGAs available in the market; making an optimized and automated approach to FPGA partitioning essential. Partitioning designs across multiple FPGAs was often done manually. Engineers would divide the design based on their experience and intuition, which was time-consuming and prone to errors. This method worked for simpler designs but became impractical as the complexity of systems grew. As digital designs became more complex, automated partitioning tools were developed. These tools aimed to optimize the partitioning process by considering logic capacity and inter-FPGA communication. Hierarchical partitioning divides the design into smaller, manageable blocks, and then partitions them further. This method improves the efficiency of the partitioning process and reduces execution time.

The Veloce Prototyping System’s (VPS) automatic timing-driven partitioning has overcome one of the most significant issues with legacy partitioners. These techniques consider the timing criticality of signals and aim to minimize the delay caused by inter-FPGA communication.

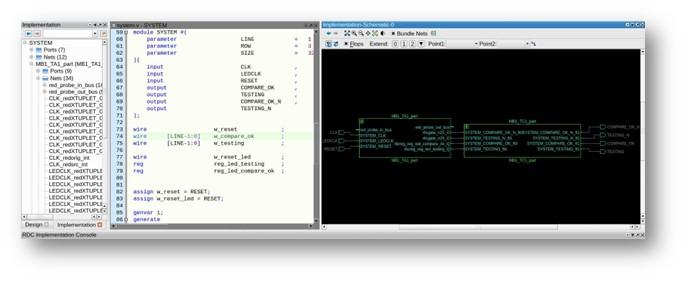

Automatic pin-muxing IP insertion, built in VPS, enables final prototypes to run at the highest possible performance by efficiently managing the I/O between FPGAs. Optimizing communication between FPGAs involves using time-division multiplexing (TDM) awareness to enable multiple signals to share the same physical connection. Dividing the communication channel into time slots, achieves this with each signal transmitted in its allocated timeslot. Both techniques enables high scalability, supporting configuration from a single FPGA to multi-blade systems, allowing users to tailor the prototyping platform to their specific project needs. The Veloce Prototyping System (VPS) auto-connect feature will let our partitioner use available FPGA connectors to interconnect them together. This saves the user time looking for the best cabling setup and enables faster delivery of the first prototype. Advanced compilation techniques enable incremental and modular compilation for multi-FPGA prototypes, enabling fast turnaround time when adding a design ECO or late probes after bitstream generation. Keeping the overall project partitioning while inserting FPGA probes is another key advantage, saving time when debugging. The Visualizer Debug Environment is the graphical engine enabling VPS users to browse their RTL design and implementation netlist during several steps of the compilation flow. The evolution of multi-FPGA partitioning continues as new challenges emerge. Future research will focus on improving partitioning algorithms scalability, integrating AI techniques for better optimization, and developing more sophisticated models to predict and mitigate timing issues. Multi-FPGA partitioning has evolved from manual, error-prone methods to sophisticated, automated techniques that consider various optimization criteria. VPS, which is 100% integrated with Veloce proFPGA CS, has also enabled various techniques to ease debug and its instrumentations. These advancements have significantly improved the efficiency and performance of multi-FPGA systems, enabling the prototyping of increasingly complex digital designs. To learn more, download the Veloce proFPGA CS factsheet or contact us at 1-800-547-3000 for details. Category: Siemens |

|

|

|||||

|

|

|||||

|

|||||