EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Linley Fall Processor Conference 2020 – Part TwoNovember 3rd, 2020 by Roberto Frazzoli

Last week, EDACafe provided a quick overview of some of the presentations which were given during the first part of this year’s Linley Fall Processor Conference, from October 20 to 22. This week we complete our coverage of the virtual event – organized by The Linley Group – by quickly summarizing some of the presentations which were given during the second part of the conference, from October 27 to 29. No shortage of innovations in this period, which is also characterized by big deals (Nvidia-Arm and AMD-Xilinx) in the processor industry. TinyML chip requirements: the Google point of view The second part of the conference was kicked off by a keynote from Peter Warden, Technical Lead of the TensorFlow Micro open source framework at Google. Warden summarized the requirements that chip vendors will need to satisfy to make the vision of TinyML come true. He foresees a future of hundreds of billions of “peel-and-stick” sensors placed on everyday objects – used for industrial monitoring, environmental monitoring, building automation, agricultural and wildlife use cases etc. – all of them capable of full-vocabulary speech recognition and/or person and gesture recognition. Linley Fall Processor Conference 2020 – Part OneOctober 27th, 2020 by Roberto Frazzoli

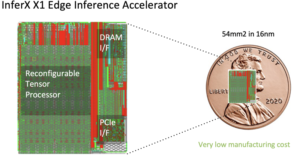

Despite the virtual format, the 2020 Fall edition of the Linley Processor Conference – organized by the technology analysis firm Linley Group – is offering its biggest program ever, with 33 technical talks across six days: October 20 to 22, and October 27 to 29. The high number of presentations confirms that these are really exciting times for innovative processing architectures. In his keynote, Linley Gwennap – Principal Analyst of The Linley Group – explained the proliferation of application-specific accelerators describing them as a way to extend Moore’s Law, since moving to the most advanced process nodes now offers little benefit. In this article, EDACafe is providing a quick overview of some of the presentations which were given during the first part of the event, mainly focusing on new announcements; next week we will complete our coverage with an overview of the second part of the conference. AI-specific architectures: Flex Logix, Brainchip, Groq, Hailo, Cornami Flex Logix’s InferX X1 chip, announced at the 2019 Linley Fall Conference, is now available. According to the company, the device is 3-18 times more efficient than Nvidia’s GPU architecture for large models with megapixel images, and is also much more efficient in terms of throughput per square millimeter of die area: it measures 54mm2 compared to 545mm2 for Nvidia Tesla T4. Flex Logix claims that the InferX X1 runs faster than Nvdia’s Xavier NX on real customer models at much more attractive prices: from $99 to $199 (1KU quantity), depending on speed grade. Brainchip, which offers a neuromorphic System-on-Chip introduced at last spring edition of the Linley Conference, has added details on “activation sparsity” and “activity regularization”. Activation sparsity is the percentage of zero-valued entries in the previous layer’s activation maps; higher activation sparsity yields fewer operations. CNNs converted to event-domain (i.e. spiking networks) automatically start at 40-60% activation sparsity due to the use of ReLU and batch normalization; Brainchip further increases activation sparsity by using activity regularization during training. Activity regularization is the process of adding more information to the loss function to balance the model’s accuracy and activation sparsity. Increasing activation sparsity, activity regularization further reduces computation. Read the rest of Linley Fall Processor Conference 2020 – Part One PLM; Ru interconnect; CNT pellicles; Intel-Sandia collaboration; 10Mbps Ethernet on a twisted pairOctober 19th, 2020 by Roberto Frazzoli

Catching up on some of the news from the last thirty days or so, this week’s focus is on both EDA-related innovations and on new process materials/equipment. Completing our updates, some application-specific news and several acquisition announcements. SoC Lifecycle Management Product lifecycle management (PLM) – a long established concept in the avionics and automotive industries – is becoming increasingly important for the development of SoCs. Two recent announcements highlight different aspects of PLM solutions targeted at SoCs: IP management and post-silicon analysis, respectively. Methodics IPLM 3.0 is the new version of the IP lifecycle management platform developed by Methodics, a company that was acquired by Perforce earlier this year. Aimed at managing the planning process of SoCs, the new platform allows what-if analysis of early design prototypes (build vs. buy vs. reuse of IP), and automates the delivery of an IP bill of materials (BoM) to development teams. Methodics IPLM also adds new security solutions addressing the concerns related to sharing IP and global IP leakage. Synopsys, for its part, has recently unveiled its Silicon Lifecycle Management (SLM) platform, described as “the industry’s first data-analytics-driven approach to optimizing SoCs from the design phase through to end-user deployment.” The Synopsys SLM platform is based on two principles: 1) gather as much useful data about each chip as possible, by adding information obtained through monitors and sensors that are embedded in the chip; 2) analyze that data throughout the chip’s entire lifecycle using analytics engines to enable optimizations at each stage of the semiconductor lifecycle, up to in-field operation. Nvidia-Arm deal: the CEOs’ perspectiveOctober 12th, 2020 by Roberto Frazzoli

With Arm priced at $40 billion, the pun was inevitable: “Somebody just said to me the other day: you paid an arm and a leg!” Nvidia’s CEO Jensen Huang recalled this joke during a ‘fireside chat’ with Arm’s CEO Simon Segars, on occasion of the Arm DevSummit – a developers’ conference that took place as a virtual event from October 6th to 8th. Despite the joke, Huang is happy with the deal: “[It’s] worth every penny and more,” he soon added. While we wait for updates on another big deal – AMD reportedly in advanced talk to buy Xilinx – the answers provided by Huang and Segars offer the official CEOs’ perspective on the Nvidia acquisition of Arm.  The “fireside chat” which took place during the Arm DevSummit [virtual event]. From left to right: moderator Rene Haas, Arm CEO Simon Segars, Nvidia CEO Jensen Huang. Image credit: Arm This deal is clearly different from most semiconductor acquisitions, usually involving two chip vendors. On the one hand, Arm is a pure-play IP licensor; on the other hand, while the business of Nvidia includes designing processor and selling chips, its technological involvement in the deal mainly concerns its AI software capabilities. “We’re going to be able to bring our capability to the Arm ecosystem, and Arm will be able to give our accelerated computing a reach like never before,” Huang said. “Nvidia has deep artificial intelligence capability, we know how to write the software of artificial intelligence,” he added. “No computing platform has the reach of Arm […], and so the combination [of the two companies] I think is just incredibly powerful that way.” Segars confirmed that Nvidia is going to bring mostly its AI software to the table: “Computers are useless without the software that runs on them,” he said, “ and we are [moving to] a world of AI where software is writing software, software is checking software, software is learning from data […]. I think between us putting the strengths of the companies together, we’re going to be able to address that.” A closer look at Mentor’s Calibre nmLVS-ReconOctober 6th, 2020 by Roberto Frazzoli

As reported by EDACafe last July, Mentor has extended their Recon technology to the Calibre nmLVS circuit verification platform. The resulting product is called Calibre nmLVS-Recon, where LVS stands for Layout Versus Schematic, and Recon stands for reconnaissance. This week we will take a closer look at this new tool with the help of Hend Wagieh, a Senior Calibre Product Manager at Mentor, a Siemens business. In the video interview that Wagieh has recently given to Sanjay Gangal from EDACafe, a number of topics concerning Calibre nmLVS-Recon have been addressed. Wagieh set up the context by briefly recapping what Calibre is about: a comprehensive platform for design automation and design analysis, which includes a number of tools for physical verification, circuit verification, parasitic extraction, yield enhancing. According to Wagieh, Calibre is used by “twenty-three out of the top twenty-five” companies designing chips worldwide.

Read the rest of A closer look at Mentor’s Calibre nmLVS-Recon Big data analytics in the spotlight at the Ansys’ IDEAS eventSeptember 28th, 2020 by Roberto Frazzoli

Designers of some of today’s most complex chips shared their experiences in a virtual event organized by Ansys on September 23rd and 24th. Called IDEAS (Innovative Designs Enabled by Ansys Semiconductor), the web-hosted conference focused on the new multiphysics simulation challenges posed by advanced technology nodes as well as by 3D ICs and chiplet-based designs. The event was used by Ansys to reiterate its approach to simulation and to highlight some of its newest solutions, such as the ones based on the SeaScape big data analytics platform. A host of new interdependent problems Let’s briefly recap some of the new problems posed by advanced technology nodes, with the help of Ansys’ white papers. As geometries have shrunk, operating voltage has also scaled down, but threshold voltages of transistors have not scaled proportionately. This has led to an increased sensitivity to voltage drop (IR), and specifically to dynamic voltage drop, which can cause changes in transistor delays and clock jitter. Small geometries also boost the stress effect of high electric fields across the dielectric, resulting in worse aging behavior due to negative bias temperature instability (NBTI). Semiconductor industry now “barely in the 18 nm generation” according to IEEESeptember 21st, 2020 by Roberto Frazzoli

Using the correct definition of technology node, today’s 5-nanometer generation actually corresponds to the 18-nanometer node. This is one of the key messages conveyed by the 2020 edition of the IEEE International Roadmap for Devices and Systems (IRDS). Building on what until 2015 was called ITRS (International Technology Roadmap for Semiconductors), the IRDS is an authoritative IEEE initiative with a proven track record of reliably predicting future technology challenges and solutions: for example, the transformation of the planar silicon gate CMOS to strained silicon, high-κ/metal-gate and FinFET was predicted by the ITRS as early as in 1998. In hundreds of content-packed pages, the recently released 2020 IRDS edition obviously covers many more topics, but the energy devoted by the authors to the node nomenclature issue – and the amount of exclamation points they used – deserve some extra attention. From metal half pitch to a marketing label Recapping the evolution of the node definitions, the IRDS authors remind readers that from 1992 to present the IC feature considered by ITRS and IRDS to name technology nodes was half pitch of the tightest metal layer, which in the past essentially coincided with the gate length. However, in the 90’s, due to the marketing pressure for a more aggressive nomenclature, the industry started using a node definition based on the average of half-pitch and gate length. Later on, some companies decided to use only the gate dimension to define the name of the technology node; and finally – according to the IRDS authors – “the technology node definition became 70% of whatever the name of the node of the previous generation was!” Therefore, the current nomenclature “has led to a complete detachment between IC features and technology nodes’ names.” As a result, the IRDS authors insist, today’s industry labeling of nodes “clearly appears completely devoted of any connection to reality.” Nvidia to acquire Arm; photonic design; 300M gate prototyping system; 4Gbps memory interface; wire aggregation; ML on Cortex-M0September 14th, 2020 by Roberto Frazzoli

Nvidia-Arm news are obviously taking center stage this week, but several interesting updates also deserve attention in areas such as EDA, prototyping, embedded systems, events, acquisitions and more. Nvidia-Arm deal Rumors have been confirmed: GPU market leader Nvidia will acquire Arm from Japanese conglomerate company SoftBank in a transaction valued at $40 billion, what is considered the largest semiconductor deal ever. The official announcement stresses the powerful pairing that brings together Nvidia’s AI computing platform with Arm’s large footprint in many diverse end products and industries, adding that Arm R&D resources in the UK will get a boost as part of the deal. In its statement, Nvidia pledges that “Arm will continue to operate its open-licensing model while maintaining the global customer neutrality that has been foundational to its success.” It remains to be seen how Arm licensees and governments’ regulating authorities will react to the news. The new situation could also potentially change the competition landscape for Risc-V open-source ISA.

SMIC news; 16Gb LPDDR5 DRAM; new approach to AI acceleration; artificial iris; VPN adoption rankingSeptember 7th, 2020 by Roberto Frazzoli

U.S.-China trade tensions are again making news this week, but there is no shortage of other updates. Among them, the introduction of the new Arm Cortex-R82, a 64-bit, Linux-capable processor targeted at next-generation enterprise and computational storage solutions It provides up to 2x performance uplift compared to previous Cortex-R generations, depending on the workload. Let’s now move to more weekly news updates. U.S. Government reportedly considering whether to add SMIC to a blacklist According to news agency Reuters, the Trump administration is considering whether to add Chinese foundry SMIC to a trade blacklist of companies, which would force U.S. suppliers of semiconductor manufacturing equipment to seek a license before shipping to the company. Reportedly, U.S. Government agencies are investigating to assess if SMIC has a relationship to the Chinese military. SMIC has responded to these media reports with a press release declaring that “the Company manufactures semiconductors and provides services solely for civilian and commercial end-users and end-uses. We have no relationship with the Chinese military. In and before 2016, SMIC had been granted Validated End-User (VEU) authorization by the BIS (Bureau of Industry and Security) and the company hosted several visits from U.S. Government officials. Any assumptions of the Company’s ties with the Chinese military are untrue statements and false accusations.” The SMIC statement concludes by declaring that “The Company is in complete shock and perplexity to the news. Nevertheless, SMIC is open to sincere and transparent communication with the U.S. Government agencies in hope of resolving potential misunderstandings.” TSMC’s roadmap; AI-based video upscaling; mobility startupsAugust 31st, 2020 by Roberto Frazzoli

The 3-nanometer node is approaching, with foundries and EDA vendors preparing to address the future demanding processes. And while “downscaling” is still a key word in chipmaking, “upscaling” is becoming an increasingly important term in video consumption, designating the conversion of old low-definition video content into HDTV or even 4K. Artificial intelligence can help in this seemingly miraculous task. Completing this week’s roundup, we continue to monitor the Silicon Valley tech environment – beyond chips – with a quick look at some mobility-related startups. TSMC’s roadmap: from N5 to N3 From August 24th to 26th, TSMC held its 2020 Technology Symposium and Open Innovation Platform (OIP) Ecosystem Forum, this year in a virtual format. On this occasion, the Taiwanese foundry provided an overview of its recent achievements and some insights on its roadmap. TSMC’s 5 nanometer N5 technology entered volume production this year, providing a 15% performance gain or a 30% power reduction, and up to 80% logic density gain over the preceding N7 technology. Building on the original N5, the company plans to ramp an enhanced N5P version in 2021, offering an additional 5% speed gain and 10% power improvement. TSMC also provided a preview of the latest member of the 5nm family – the N4 process. N4 is expected to offer further PPA improvements with reduced mask layers, while leveraging the 5nm design ecosystem. The N4 process is scheduled to start risk production in fourth quarter of 2021, with volume production in 2022. As for the next node, TSMC claimed to be “on track” with the development of its N3 process, expected to offer up to 15% performance gain, up to 30% power reduction, and a logic density gain up to 70% over N5, also thanks to “architectural innovations”. Major EDA vendors are already preparing to support N3: the achievement of TSMC certification for this future process node has recently been announced by Ansys, Cadence and Synopsys. |

|

|

|||||

|

|

|||||

|

|||||