EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. EDA updates; Indy Autonomous Challenge; Qualcomm-Nuvia deal; RRAM-based edge learning; robomorphic computingJanuary 25th, 2021 by Roberto Frazzoli

Will we see tech students spraying Champagne during the awards ceremony at the Indy Autonomous Challenge next October? What is sure is that the race initiative confirms a strong academic commitment to autonomous vehicle research. Meanwhile, Hyundai Motor and Apple are reportedly planning to sign a partnership deal on autonomous electric cars by March and start production around 2024 in the United States. More about the Indy race below, after some EDA news. Other updates this week concern CPUs, machine learning, and robotics. EDA updates: Ansys, Siemens Ansys has recently launched its new HFSS Mesh Fusion. Available in Ansys HFSS 2021 R1, the new solution enables fully-coupled simulation of entire, complex electromagnetic systems. It combines integrated circuits, packaging, connectors, printed circuit boards, antennas and platform in a single Ansys HFSS analysis to predict electromagnetic interactions. The EDA business of Siemens – formerly Mentor – has announced that its tools for the verification of analog/mixed-signal circuits are now qualified for early design starts on Samsung Foundry’s new 3nm Gate All Around process technology. Early-stage AMS designs can now be verified using the Analog FastSpice (AFS) platform on Samsung’s most advanced process technology. Intel’s new CEO: comments from media and analystsJanuary 18th, 2021 by Roberto Frazzoli

Comments abound on last week’s Intel news announcing the appointment of Pat Gelsinger as the company’s new chief executive officer, effective Feb. 15, 2021. The official press release is quick to underline that the announcement “is unrelated to Intel’s 2020 financial performance” and that “the company has made strong progress on its 7nm process technology”, implicitly dismissing the notion of a reaction to a problem. But all observers are obviously interpreting this sudden CEO change as a move aimed at recovering competitiveness after a lackluster period that was becoming worrisome for the investor community. For example, EDACafe last week briefly reported about a letter sent to Intel by Third Point, complaining not only about Intel’s well-known delay in moving to the 7-nanometer node, but also about its loss of many talented employees, certain questionable acquisitions, and more. Observers unanimously express positive judgements on Gelsinger – see, for example, the article from Tirias Research’s Jim McGregor on EETimes. Gelsinger has an engineering background and spent thirty years of his career at Intel, which he left in 2009 to join EMC as President and COO. From 2012 to present, he served as CEO of virtualization leader VMware. More bio details about him can be found in this note to all Intel employees. So, Gelsinger sounds like a great choice; but what about his new strategy? Staying IDM versus going fabless Given the difficulties that Intel is currently experiencing in keeping pace with foundries, a key point that Gelsinger will need to address is the choice between retaining Intel’s IDM identity – in other words, keeping the fabs – or embracing the fabless model, which would basically mean outsourcing the manufacturing to TSMC. The obvious parallel is with what AMD did back in 2008-2009, when it sold its fabs to the entity that later became GlobalFoundries. On this point, Robert Maire from Semiconductor Advisors wrote some interesting comments on SemiWiki. According to Maire, AMD’s example is not a good one: “We think that this is not a good comparison. AMD did not have the minimum critical mass needed to support a fab and all the R&D that goes along with it. Intel has the size, scope and market needed to support the associated spend. The basis of the problem is not economic as it was with AMD; it is an execution/technical problem that Intel has encountered.” Read the rest of Intel’s new CEO: comments from media and analysts EDA Q3 figures; Achronix to list on Nasdaq; automotive chip shortage; SMIC added to Entity List; AI updatesJanuary 11th, 2021 by Roberto Frazzoli

Boston Dynamics dancing robots seem to be a good topic to start this news roundup, the first of 2021. They can be enjoyed by watching this video, created by the robotics company “to celebrate the start of what we hope will be a happier year”. Let’s now move straight to this week’s updates. EDA revenue growth in Q3 2020 According to the Electronic System Design Alliance, EDA industry revenue increased 15% in Q3 2020 to $2,953.9 million, compared to $2,567.7 million in Q3 2019, with all categories logging significant gains. The four-quarter moving average, which compares the most recent four quarters to the prior four quarters, rose by 8.3%. The product category showing the strongest growth was IP, with a 25.8% revenue increase. In terms of regions, Asia Pacific reported the best results with a 26.4% growth. The EDA companies tracked by ESD Alliance employed 47,087 people in Q3 2020. 2020 year in reviewDecember 31st, 2020 by Roberto Frazzoli

Needless to say, the Covid-19 pandemic turned 2020 into a nightmare. It also changed most people’s working life, shutting down in-person gatherings and replacing them with virtual events. Still, 2020 was an exciting year for the semiconductor industry and related segments – in terms of market growth, technological innovation, and overall evolution. As we approach the year’s end, let’s try to briefly summarize some of the major events and themes that characterized the last twelve months. A record year for acquisitions The most apparent characteristic of 2020 was definitely the large number of sizeable acquisitions, either announced or completed. This obviously refers to the Nvidia-Arm, AMD-Xilinx, Analog Devices-Maxim and Infineon-Cypress deals, but also to many other smaller yet significant acquisitions. During 2020, EDACafe reported about approximately fifty of them. Risc-V Summit 2020 showcases a growing ecosystem and a wider application spectrumDecember 14th, 2020 by Roberto Frazzoli

The virtual event held from December 8 to 10 offered several updates on topics such as core design verification, standard extensions enabling new applications, and open-source EDA tools, with contributions from both the industry and academic research Almost one quarter (23 percent) of all new IC/ASIC or FPGA projects incorporate a Risc-V processor in their design, according to the 2020 Wilson Research Group functional verification study, a survey – available here and here – commissioned by Mentor. In fact, 2020 has been a year of growth for this open instruction set architecture, as underlined by Calista Redmond, CEO of Risc-V International, in her keynote at this year’s Risc-V Summit. Adoption has grown in all industry segments, including embedded, AI, IoT, HPC etc. Initiatives carried out by Risc-V International in 2020 include ratification of the processor trace specification, a new algorithm that allows to see what instructions a core is executing; a partnership with GlobalPlatform, the standard for secure digital services and devices; new alliances, training programs, and more. The association also launched the ‘Risc-V Exchange’, with more than 124 Risc-V cores and SoCs and developer boards along with 129 Risc-V software applications and tools. Plans for 2021 include public review for several new standard extensions. Let’s now take a quick look at some of the innovations presented at the Summit. All the papers briefly quoted here can be accessed from the event website.

Research in electronic devices takes center stage at 2020 IEDM eventDecember 7th, 2020 by Roberto Frazzoli

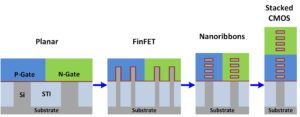

Running as a virtual event from Saturday through Friday, December 12-18, this years’ edition of IEDM (IEEE International Electron Devices Meeting) will offer a mix of live-streamed video content (such as the plenary presentations, panel discussion and career session) and on-demand pre-recorded presentations, with a schedule of live Q&A sessions. The event’s program includes more than 220 papers, plus tutorials and short courses. Part of the papers will cover emerging topics through six focus sessions: cryogenic electronics; GaN and SiC; future interconnect; technologies enabling 5G and beyond; energy harvesting and wireless power transmission; DTCO of advanced logic and memory. As a quick preview of the event, let’s now have a look at some of the technical highlights from the presentations. Intel’s future transistor: stacked NMOS-on-PMOS nanoribbons Next generation FET architectures for logic devices are a much-debated issue in the industry, and at IEDM Intel researchers will present a new candidate: a NMOS-on-PMOS transistor built from multiple self-aligned stacked nanoribbons. This architecture employs a vertically stacked dual source/drain epitaxial process and a dual metal gate fabrication process, enabling different conductive types of nanoribbons to be built so that threshold voltage adjustments can be made for both top and bottom nanoribbons. According to Intel, this approach combines excellent electrostatics (subthreshold slope of <75 mV/dec) and DIBL (Drain Induced Barrier Lowering, <30mV/V for gates ≥30nm) with a path to significant cell size reduction due to the self-aligned stacking. These devices were used to build a functional CMOS inverter with well-balanced voltage transfer characteristics.  The evolution of transistor architectures from planar, to FinFETs, to nanoribbons and to a 3D CMOS architecture. Credit: Intel Read the rest of Research in electronic devices takes center stage at 2020 IEDM event IC market forecasts; new edge AI chips; automotive softwareNovember 30th, 2020 by Roberto Frazzoli

The so-called ‘semiconductor renaissance’ is tightly related to the artificial intelligence boom, so this week the latest IC market growth figures fit well with the updates about new edge AI chips from well-funded startups. Automotive software is also making news, along with some last-minute additions to the virtual events calendar. Intel still number one semiconductor supplier in 2020 According to the latest forecast from market research firm IC Insights, Intel will keep its number one semiconductor supplier ranking in 2020. As noted by the analysts, this year the Covid-19 pandemic spurred an acceleration of the worldwide digital transformation resulting in a robust semiconductor market growth. In total, the top-15 semiconductor companies’ sales are forecast to jump by 13% in 2020 compared to 2019. In contrast, in 2019 the top-15 semiconductor suppliers registered a collective 15% decline in sales. IC Insights expects two new entrants into the top-15 semiconductor sales ranking for this year: MediaTek and AMD. Forecasted sales increases for these companies are 35% and 41%, respectively. Peculiar to this list is the inclusion of Apple – which uses its chips only in its own products – and of foundries like TSMC – which mean that some sales are double counted. Read the rest of IC market forecasts; new edge AI chips; automotive software Intel FPGA news; Ferroelectric Memory; Micron’s 176-layer NAND; TSMC’s Phoenix fab; Tesla security issueNovember 23rd, 2020 by Roberto Frazzoli

Step-by-step instructions on how to steal a Tesla are probably this week’s most curious news, even accompanied by a video (by the way: the security flaw has already been fixed by Tesla). But first, the usual weekly news summary. PSS 2.0 draft available for public review Accellera has announced the availability of the Portable Test and Stimulus Draft Standard 2.0 (PSS) for public review. New major features intend to improve the usability of the standard and expand its portability and flexibility to a broader class of verification challenges. Public review was opened on November 18 and will close on December 18, 2020. Reactions to AMD-Xilinx deal; more acquisitions; upcoming eventsNovember 16th, 2020 by Roberto Frazzoli

Acquisitions make up most part of this week’s article. Catching up on some of the news from the last thirty days, the AMD-Xilinx deal inevitably stands out – clearly no longer as a fresh update, but as a topic that deserves some reflections. We will therefore take a look at some of the comments that have been published by the media. Coincidentally, several more acquisitions were announced over the past few weeks – clearly much smaller, but still significant in their respective markets. AMD-Xilinx deal: some comments from the media With the acquisition of Xilinx, AMD hopes to create “the industry’s High Performance Computing leader”. The future scenario for HPC silicon, therefore, could be characterized by three major competitors: Nvidia (with the recent addition of Arm), Intel (which bought Altera in 2015), and the AMD-Xilinx combination. Sally Ward-Foxton on EETimes asks a question that is key to figure out the future competitive landscape: “Is AMD trying to build a complete data center computing platform, similar to what Nvidia is trying to do with Arm?” She also observes that “Nvidia has plans to combine Mellanox’ SmartNICs with Arm CPU accelerators and VLIW acceleration blocks to make what it calls a DPU (…). AMD doesn’t have anything in this area, but Xilinx does — a SmartNIC platform based on its FPGAs was launched this spring.” Commenting the new scenario, Kris Kachris on SemiWiki anticipates less freedom of choice for customers: “We are moving on the era of Heterogeneous Data Processing Platforms where computing platforms will include SmartNICs, multi-core processors and hardware accelerators and the user will have to select a complete solution instead of mix-and-match. Intel, AMD and Nvidia will offer complete computing platforms with their own proprietary accelerators and SmartNICs. (…) the option to select the best of each world will not be feasible any more or at least it will be more challenging.” Read the rest of Reactions to AMD-Xilinx deal; more acquisitions; upcoming events New testing challenges take center stage at the International Test Conference 2020November 10th, 2020 by Roberto Frazzoli

Smaller process geometries, multibillion-transistor designs, zero-defect requirements, emerging memories, new security threats: technology advancements and evolving application constraints make chip testing increasingly challenging and increasingly important. Researchers around the world, in the semiconductor industry and in the academia, struggle to overcome these new challenges – aiming to ensure effective chip testing while preserving the best possible PPA results and optimizing the use of testing resources. Every year, the International Test Conference offers a wide selection of some of the best research works in this area, and the 2020 edition – which took place as a virtual event from November 3rd to 5th, sponsored by IEEE and the IEEE Philadelphia Section – was no exception. This week, EDACafe quickly browses through the proceedings of ITC 2020, peeking into a few sample papers just to give a sense of the new challenges confronting test engineers, and a taste of the new solutions that are being proposed. Read the rest of New testing challenges take center stage at the International Test Conference 2020 |

|

|

|||||

|

|

|||||

|

|||||