EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. TSMC-EDA updates; Google’s AI-based chip layout tool; new Altera FPGAs; double-faced GaN wafersSeptember 30th, 2024 by Roberto Frazzoli

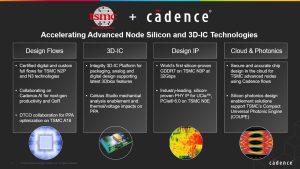

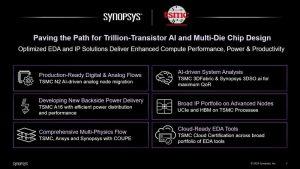

Let’s start by briefly mentioning two U.S. CHIPS Act updates. Polar Semiconductor will receive up to $123 million in direct funding to expand and modernize the company’s manufacturing facility in Bloomington, Minnesota. The investment is expected to nearly double the U.S. production capacity of sensor and power chips. The U.S. government has also launched the National Semiconductor Technology Center’s (NSTC) Workforce Center of Excellence (WCoE), with an expected $250 million investment over ten years, to support education programs that address key skills and workforce gaps in the semiconductor industry. The first cohort of awardees consists of the following organizations: American Federation of Teachers Educational Foundation, Idaho Technology Council, Maricopa County Community College District, Rochester Institute of Technology, Texas A&M University, University of California Los Angeles, University of Illinois Urbana-Champaign. Latest EDA updates from TSMC OIP Forum North America On occasion of TSMC OIP Forum North America, held in Santa Clara on September 25, the major EDA vendors announced their latest tool certifications and new collaborations with the Taiwanese foundry. In general, tool certifications mainly concern TSMC’s N2 process, and areas of collaboration include backside power delivery for the foundry’s A16 process, 3D packaging, multiphysics simulation, IP, cloud-based EDA and more. Here are the announcements from Ansys, Cadence, Siemens and Synopsys. The agenda of the TSMC event, with abstracts of the presentations, can be found here. Below, two charts summarizing the news from Cadence and Synopsys.

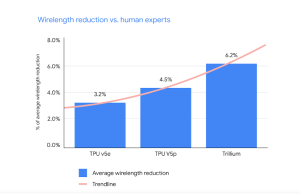

New release of Silvaco’s TCAD platform Silvaco’s 2024 TCAD Baseline Release simulation platform includes digital twin modeling and provides support for planar CMOS, FinFET and Gate-All-Around (GAA) transistor technologies, enabling semiconductor companies to accelerate technology development. Updates on Google’s AI-based chip layout tool Google DeepMind has recently published an article providing updates on its chip layout tool using an AI technique called reinforcement learning. The tool now has a name: AlphaChip. Among other things, the researchers released a pre-trained checkpoint, sharing the model weights, and disclosed some performance figures in terms of average wirelength reduction across three generations of Google’s Tensor Processing Units (TPUs), compared to placements generated by the TPU physical design team (see chart). Google also unveiled that MediaTek used AlphaChip to accelerate development of their most advanced chips — like the Dimensity Flagship 5G used in Samsung mobile phones. Google researchers believe AlphaChip has the potential to optimize every stage of the chip design cycle, from computer architecture to manufacturing. The checkpoint on GitHub includes pre-training instructions for users who want to pre-train AlphaChip on their own chip blocks, which Google strongly recommends. Altera’s Agilex 3 FPGAs and new software release At its annual developer’s conference, Altera revealed new details on its Agilex 3 “power- and cost-optimized” FPGAs for embedded and intelligent edge applications, and announced new development kits and software support for its Agilex 5 FPGAs. Agilex 3 FPGAs, which offer densities ranging from 25K to 135K logic elements, feature an on-chip dual Cortex A55 ARM hard processor subsystem with a programmable fabric infused with AI capabilities. The new FPGAs add security enhancements over the previous generation, including bitstream encryption, authentication, and physical anti-tamper detection. Agilex 3 FPGAs leverage Altera’s HyperFlex architecture to provide a 1.9×1 performance improvement over the previous generation. Additional system performance is achieved through integrated high-speed transceivers operating up to 12.5 Gbps and added support for LPDDR4 memory. Altera also announced the newest features offered in the upcoming Quartus Prime Pro 24.3 release of its software, which unlocks more devices within the Agilex portfolio and enables improved support for embedded applications. The upcoming release will enable users to start designing Agilex 5 FPGA D-series, which targets a broader range of use cases compared to Agilex 5 FPGA E-series. This software release also includes support for embedded applications that employ either an integrated hard-processor subsystem or Altera’s Risc-V solution, the Nios V soft-core processor that can be instantiated in the FPGA fabric. Lastly, the company offers Agilex 5 FPGA design examples that showcase Nios V capabilities such as lockstep, full ECC, and branch prediction. SK hynix’s 36GB 12-layer HBM3E SK hynix has begun mass production of what it claims is the world’s first 12-layer HBM3E product with 36GB, the largest capacity of existing HBM to date. Previously, the maximum capacity of HBM3E was 24GB from eight vertically stacked 3GB DRAM chips. With this latest development, SK hynix has increased the capacity by 50% by stacking twelve layers of 3GB DRAM chips at the same total thickness as the previous eight-layer product. To achieve this, the company made each DRAM chip 40% thinner than before, and stacked vertically using TSV technology. The company said it solved structural issues that arise from stacking thinner chips higher by applying its core technology, the Advanced MR-MUF (Mass Reflow Molded Underfill) process, which injects liquid protective materials between the stacked chips, instead of laying film-type materials. GaN crystal polarization enables HEMTs and LEDs on opposite sides of the same wafer Researchers from Cornell University and Polish Academy of Sciences have built a chip that takes advantage of the different properties shown by the two sides of a Gallium nitride wafer. The team succeeded in building a high electron mobility transistor (HEMT) on one side that drives LEDs on the other side. As the researchers explained, Gallium nitride is unique among wide-bandgap semiconductors because it has a large electronic polarization along its crystal axis, which gives each of its surfaces dramatically different physical and chemical properties. The gallium, or cation, side has proved useful for photonic devices such as LEDs and lasers, while the nitrogen, or anion, side can host transistors. In contrast, there’s no additional functionality from using both sides of a silicon wafer because they are basically identical. A possible application for the “dualtronic” GaN chip is microLEDs: fewer components, occupying a smaller footprint and requiring less energy and materials, and manufactured quicker for lower cost. The researchers, however, envision further integration possibilities with the addition of piezoelectric resonators and lasers. New version of MIPI automotive SerDes physical-layer interface The MIPI Alliance has released MIPI A-PHY v2.0, the new version of the automotive high-speed asymmetric SerDes physical-layer interface. Version 2.0 doubles the maximum available downlink data rate from 16 Gbps to 32 Gbps on a single channel, and adds an additional uplink gear with an eight-fold speed boost to support up to 1.6 Gbps. These enhancements are designed to support the higher bandwidth requirements for zonal and other emerging architectures in next-generation vehicles. |

|

|

|||||

|

|

|||||

|

|||||