EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. China reportedly readying semi subsidies; IBM-Rapidus partnership; Risc-V updates; 150 TOPS/W edge AI acceleratorDecember 20th, 2022 by Roberto Frazzoli

Several updates concerning U.S.-China tensions have been in the news over the last few days. Risc-V is another major theme of this news roundup, with product announcements from the recent Risc-V Summit. And one more AI startup is raising the bar for energy efficiency. Will the ‘chip war’ escalate hitting older nodes? While export controls on Western technologies have so far focused on the most advanced process nodes, the ‘chip war’ between the U.S. and China could potentially escalate and hit older nodes, according to a TechInsights analyst quoted by Reuters. The premises for this analysis can be found in two press reports: on the one hand, China is reportedly working on a $143 billion support package for its semiconductor industry, to counter U.S. moves aimed at slowing its technological advances; on the other hand, Chinese foundry SMIC is reportedly ramping up production of 28-nanometer chips, an old node still widely used in automotive, weapons and IoT applications. While subsidies would likely benefit Chinese equipment manufacturers – such as Naura, Advanced Micro-Fabrication Equipment and Kingsemi – the concern of TechInsights is that SMIC and other chipmakers in China could use government subsidies to sell 28-nanometer chips at a low price, flooding this market segment and wiping out global competition.

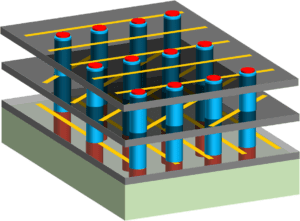

Another recent update is that the U.S. government has added Chinese memory chipmaker YMTC and twenty-one “major” Chinese players in the artificial intelligence chip sector to a trade blacklist; other notable companies in this group include Cambricon, CETC and PXW. A couple of updates concern the implementation of Japan’s and European Union’s semiconductor support plans. IBM and Rapidus – the recently founded semiconductor company funded by the Japanese Government – have announced a partnership which will include the development of IBM’s 2-nanometer node technology for implementation by Rapidus at its fab in Japan. Rapidus scientists and engineers will work alongside IBM Japan and IBM researchers at the Albany NanoTech Complex (New York). As for Europe, Intel has reportedly backed away from its original target of opening a chip factory in the German city of Magdeburg in the first half of 2023, asking for more public subsidies. Intel cited surging energy and raw materials prices causing the budgeted fab cost to increase from the original 17 billion euros to 20 billion euros. Risc-V updates from the Risc-V Summit The Risc-V ecosystem keeps expanding, in terms of silicon devices, IP, development tools etc. Here is a quick overview of some of the new products introduced at the recent Risc-V Summit. Andes announced the new member of its AndesCore 45-Series, the AX45MPV with Linux multicore and 1024-bit vector processing capabilities. The AX45MPV targets the applications with large volumes of data such as datacenter AI inference and training, ADAS, AR/VR, computer vision, cryptography, and multimedia. Breker has unveiled the Integrity FASTApps Portfolio, a library of automated test generation intellectual property elements targeting difficult-to-verify processor core and SoC scenarios. The FASTApps provide commercial-grade, high-coverage verification for Risc-V processor cores and the SoC platforms that use them. Codasip launched SecuRISC5, an initiative to provide its customers with safe and secure custom compute using highly verified reference designs combining Codasip IP and third-party technology. Following the recent acquisition of Cerberus Security Labs, Codasip is accelerating security developments for its Risc-V processor IP and plans to make security reference designs available in 2023. Imperas introduced the latest updates to ImperasDV to support the rapid growth in Risc-V verification. Updates include the extensions of verification IP options to include riscvISACOV, a set of SystemVerilog source functional coverage libraries; and the addition of architectural validation test suites for RV32E, RV64E, Zc, and Zmmul specifications. The company has also announced that MIPS has selected Imperas to provide advanced Risc-V processor verification tools. Intel announced new ecosystem partners and new features for its ‘Pathfinder for Risc-V’ initiative, a pre-silicon development environment that supports IP selection via testing for compatibility and performance, as well as early-stage software development using FPGA and simulator platforms. The new features include unification of the Starter & Professional Editions; static kernel debug for users wanting to debug the Linux kernel; multi-core support via SMP Linux; a new FMC add-on board enabling new I/O interfaces and simplifying connectivity; a new Cyclone 10 GX development board. Microchip previewed its PolarFire 2 FPGA silicon platform and Risc-V-based processor subsystem and software suite roadmap. The PolarFire 2 family will improve the performance and power-efficiency curve and add new Risc-V-based high-performance compute elements. It will be supported by a design tool set that eliminates the need for algorithm developers to understand the intricacies of the underlying FPGA hardware. MIPS unveiled availability of the eVocore P8700, which the company claims is the industry’s highest performance, most scalable Risc-V multiprocessor IP. The P8700 is the first Risc-V IP core that provides out-of-order processing and coherent multi-threaded, multi-core, multi-cluster scalability. Mobileye has licensed the new MIPS eVocore P8700 multiprocessors for its latest generation of EyeQ System-on-Chips for ADAS and autonomous vehicles. Siemens announced that its Sokol Flex OS software now supports Risc-V embedded development. Based on the popular, open-source Yocto Project industry standard, Siemens‘ Sokol Flex OS helps embedded developers create customized, Linux-based systems for Risc-V architectures. Ventana introduced its Veyron family of high performance Risc-V processors. Described as a “data center class” CPU, the Veyron V1 is the first member of the family, and – according to the company – the highest performance Risc-V processor available today. It will be offered in the form of high performance chiplets and IP. An analyst opinion on this processor is available here. XMOS revealed a Risc-V compatible architecture for the fourth generation of its xcore processor platform, targeted at IoT applications. The solution delivers the flexibility to define entire systems in software. In-memory computing updates: EnCharge AI, Rain Neuromorphics Startup EnCharge AI has emerged from stealth and announced it has raised $21.7M in Series A financing. The company’s charge-based in-memory computing technology, targeted at edge AI applications, was originally born out of DARPA and U.S. Department of Defense funded R&D. EnCharge claims “orders-of-magnitude higher compute efficiency and density” compared to both best-in-class digital accelerators, such as GPUs or TPUs, and optical or analog computing. Its test chips and hardware can achieve over 150 TOPS/W for 8-b compute. Offering includes a software stack. In a blog post, Rain Neuromorphics has announced it has been granted a patent on a new in-memory computing architecture for AI enabling ultra-high dimensional sparse matrix multiplication using emerging 3D memory technology. |

|

|

|||||

|

|

|||||

|

|||||