EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Nvidia’s innovations; secure design; cloud-based EDA; Risc-V tools; early-stage investmentsMarch 25th, 2022 by Roberto Frazzoli

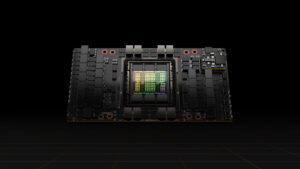

Both Nvidia and Arm are in the news this week, obviously for unrelated reasons after the proposed acquisition deal collapsed. Nvidia keeps introducing impressive innovations at an impressive pace, raising the bar for contenders. Meanwhile, Arm keeps preparing for its IPO – expected to value the company at $60 billion – with SoftBank reportedly planning to pick Goldman Sachs as the lead underwriter. Nvidia GTC updates At its recent GTC event, Nvidia introduced a host of new products and innovations mostly targeted at AI-powered data centers; here we will only provide an extremely brief overview. As for GPUs, the company launched its new Hopper architecture, claiming an order of magnitude performance leap over its predecessor Ampere architecture. Nvidia also announced the first Hopper-based GPU, the H100, an 80 billion transistors chip built using a TSMC 4N process, offering nearly 5 terabytes per second of external connectivity and 3 terabytes per second of memory bandwidth. Among the innovations introduced by the H100 is a new Transformer Engine (devoted to the Transformer model for natural language processing); the second generation of the Secure Multi-Instance GPU technology; the fourth generation of NVLink; new DPX instructions to accelerate dynamic programming. A 71-page white paper on the H100 architecture can be downloaded from this web page. As for data center CPUs, Nvidia announced its first Arm Neoverse-based processor, called ‘Grace CPU Superchip’, comprising two CPU chips coherently connected over NVLink-C2C, a new high-speed, low-latency, chip-to-chip interconnect. The device integrates 144 Arm cores, reaching an estimated performance of 740 on the SPECrate 2017_int_base benchmark. Another announcement from the GTC event concerns NVLink-C2C, a chip-to-chip and die-to-die interconnect, open to custom silicon integration. NVLink-C2C enables coherent interconnect bandwidth of 900 gigabytes per second or higher. In addition to it, Nvidia will also support the Universal Chiplet Interconnect Express (UCIe) standard announced earlier this month. Recent updates also include Nvidia reportedly interested in exploring chip manufacturing with Intel Foundry Services.

Cadence selected for DoD secure design program Cadence has been selected to participate in the Microsoft Rapid Assured Microelectronics Prototypes (RAMP) Phase II initiative. The RAMP program is an initiative within the U.S. Department of Defense (DoD) focused on the advancement of state-of-the-art, secure microelectronics design methods. As part of the Phase II program, Cadence is providing best practice recommendations and security integrations with its digital and verification design flows for advanced SoC designs from select defense industrial base prototype designs. The plan is to have the secure design environment integrated into the Microsoft Azure-based deployment infrastructure to support state-of-the-art microelectronics development for mission-critical aerospace and defense applications. Cloud-based EDA updates: Cadence, Ansys GlobalFoundries has qualified the Cadence digital solution on Amazon Web Services (AWS) for its 22FDX platform. Among early users, Sweden-based Xenergic leverages the Cadence Cloud Passport to tape out test chip featuring Tensilica Fusion F1 DSP and low-power memories on the GF 22FDX platform. Ansys customers will have automatic cloud access to the latest 3rd Gen AMD Epyc processors with AMD 3D V-Cache technology, available on Microsoft Azure HBv3 VMs. Ansys Cloud, the managed cloud service provided by Ansys and enabled on Azure, will automatically upgrade to offer the ability to use the latest AMD chips. The new Azure offering has been designed specifically to accelerate CAE workflows. In early testing by Azure, the company saw up to 80% improvement in large-scale computational fluid dynamics simulations and up to 50% improvement in explicit finite element analysis crash tests. Risc-V development updates: Segger, IAR Systems Germany-based Segger has released Version 6 of its ‘Embedded Studio for Risc-V’, featuring real-time memory management to improve efficiency and response time when allocating and freeing up memory as needed by hard real-time in applications written in C++. The new version supports all common Risc-V 32-bit and 64-bit cores. As explained by the company, C++ applications require a lot of memory allocation and deallocation behind the scenes. Fast responses bring true real-time to embedded systems programmed in C++. Sweden-based IAR Systems has joined the Risc-V Foundation, adding its IAR Embedded Workbench to the Risc-V ecosystem. Early-stage investor Imec.xpand keeps expanding Imec.xpand, the early-stage investment initiative of Belgian research institute Imec, has recently announced the first closing of its second fund at EUR 150 million in committed capital. The first Imec.xpand fund invested in sixteen companies that, so far, raised close to EUR 350 million in additional financing from other investors. Today the Imec.xpand portfolio includes – among other companies – PsiQuantum, Spectricity, Celestial AI, Fabric8labs and Axelera AI. The fund aims at reaching a EUR 250 million target. Smartphones to provide one-meter positioning accuracy Trimble RTX GNSS technology is now available on Qualcomm’s Snapdragon 8 Gen 1 and Snapdragon 888 Mobile Platforms, enabling smartphone manufacturers, service providers and application developers to provide users of premium Android smartphones with one meter (about 3 feet) positioning accuracy. Potential applications include car navigation with lane-level guidance. New power supply ICs achieve better response with lower capacitance QuiCur, a new power supply technology introduced by Rohm, improves the load transient response characteristics of DC/DC converter ICs (switching regulators) and LDOs (linear regulators). According to Rohm, QuiCur solves the two problems of conventional power supply IC feedback circuits when pursuing maximum response performance: the unusable region generated in the frequency range lower than the unstable area; and variations in the zero-cross frequency due to the output capacitance, by fully dividing the roles of signal processing for response speed (control system) and voltage stability (compensation system). The first problem was solved by utilizing a dedicated error amp that does not generate an unusable area in the feedback circuit. For the second problem, Rohm adopted a dedicated second-stage error amp and introduced a technology that allows the amplification factor (gain) to be adjusted by current drive. Although the zero-cross frequency may vary depending on the connected output capacitance, by adjusting the amplification factor, the zero-cross frequency can always be set on the boundary line between the unstable and stable control regions. According to the company, QuiCur alone can reduce the output capacitance to the microFarad order of magnitude; if combined with Rohm’s Nano Cap technology, capacitance can be brought down to nanoFarads. A detailed 27-slide white paper on QuiCur is available here. Acquisitions Korea-headquartered Semifive has acquired Analog Bits (Sunnyvale, CA), a provider of low-power mixed-signal IP solutions. Upcoming events TinyML Summit 2022 will take place as an in-person event from March 28 to March 30 in Burlingame, CA. In conjunction with the Summit, the tinyML Research Symposium 2022 will be held on Monday, March 28. |

|

|

|||||

|

|

|||||

|

|||||