Both Nvidia and Arm are in the news this week, obviously for unrelated reasons after the proposed acquisition deal collapsed. Nvidia keeps introducing impressive innovations at an impressive pace, raising the bar for contenders. Meanwhile, Arm keeps preparing for its IPO – expected to value the company at $60 billion – with SoftBank reportedly planning to pick Goldman Sachs as the lead underwriter.

Nvidia GTC updates

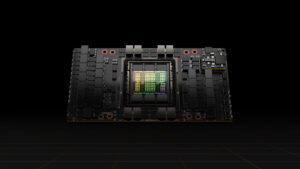

At its recent GTC event, Nvidia introduced a host of new products and innovations mostly targeted at AI-powered data centers; here we will only provide an extremely brief overview. As for GPUs, the company launched its new Hopper architecture, claiming an order of magnitude performance leap over its predecessor Ampere architecture. Nvidia also announced the first Hopper-based GPU, the H100, an 80 billion transistors chip built using a TSMC 4N process, offering nearly 5 terabytes per second of external connectivity and 3 terabytes per second of memory bandwidth. Among the innovations introduced by the H100 is a new Transformer Engine (devoted to the Transformer model for natural language processing); the second generation of the Secure Multi-Instance GPU technology; the fourth generation of NVLink; new DPX instructions to accelerate dynamic programming. A 71-page white paper on the H100 architecture can be downloaded from this web page. As for data center CPUs, Nvidia announced its first Arm Neoverse-based processor, called ‘Grace CPU Superchip’, comprising two CPU chips coherently connected over NVLink-C2C, a new high-speed, low-latency, chip-to-chip interconnect. The device integrates 144 Arm cores, reaching an estimated performance of 740 on the SPECrate 2017_int_base benchmark. Another announcement from the GTC event concerns NVLink-C2C, a chip-to-chip and die-to-die interconnect, open to custom silicon integration. NVLink-C2C enables coherent interconnect bandwidth of 900 gigabytes per second or higher. In addition to it, Nvidia will also support the Universal Chiplet Interconnect Express (UCIe) standard announced earlier this month. Recent updates also include Nvidia reportedly interested in exploring chip manufacturing with Intel Foundry Services.