EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Vertical FET; emerging memories; TSMC’s capex; DAC figuresJanuary 19th, 2022 by Roberto Frazzoli

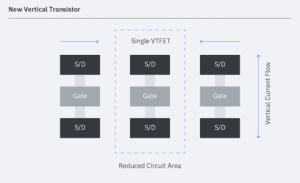

Later this year the industry will celebrate the tenth anniversary of the publication of AlexNet, widely considered the starting point of the current neural network boom. But another celebration took place recently: the fiftieth anniversary of the microprocessor. The magazine “IEEE Micro” has devoted a special issue to this event, hosting – among others – an article from Federico Faggin telling the story of the Intel 4004. EETimes also turned fifty recently, and veteran semiconductor analyst Malcolm Penn celebrated this anniversary by contributing three articles on the history of Silicon Valley: here are Part One, Part Two and Part Three. Let’s now quickly catch up on some of the news updates from December and early January. IBM and Samsung develop the vertical FET IBM and Samsung Electronics have jointly announced a new vertical transistor architecture called VTFET that promises further scaling beyond nanosheet. As explained in this blog post, vertically orienting the current flow removes the horizontal constraints to gates, spaces and contacts dimensions. In this way, the Contacted Gate Pitch can be scaled while maintaining healthy size for all these features. Specifically, the VTFET allows to use larger source/drain contacts to increase the current on the device; the gate length can be selected to optimize device drive current and leakage; and the spacer thickness can be independently optimized for lower capacitance. Another key VTFET feature is the ability to use shallow trench isolation for adjacent circuits, to achieve a Zero-Diffusion Break (ZDB) isolation, with no loss of active-gate pitches. By comparison, the density of conventional lateral-transport FET circuitry is affected by double or single-diffusion breaks required for circuit isolation, which affects the ability to further shrink.

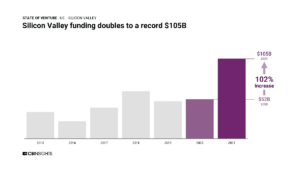

Advancements in emerging memories: FeRAM, STT-MRAM, UltraRAM At the recent 2021 edition of IEDM (IEEE International Electron Devices Meeting), French research institute CEA-Leti presented a new type of ferroelectric RAM (FeRAM) that is fully CMOS compatible and scalable to advanced nodes – unlike its PZT-based counterpart. Key to CMOS compatibility is the BEOL integration of HfO2-based ferroelectric capacitors. The new 16-kbit device is also compatible with solder reflow. Also at IEDM 2021, Renesas announced the development of two technologies that reduce the energy and voltage application time for the write operation of spin-transfer torque magnetic RAM (STT-MRAM). On a 20Mbit test chip, a 72 percent reduction in write energy and a 50 percent reduction in the voltage application time were confirmed. The new technologies are: 1) a self-termination write scheme with slope pulse application, in which the write pulse is automatically and adaptively terminated due to write characteristics of each memory cell; 2) a write sequence to optimize the number of bits, to which write voltage is applied simultaneously. Researchers from UK-based Lancaster University have demonstrated the possibility of manufacturing a memory called UltraRAM on silicon wafers – instead of GaAs wafers. UltraRAM, a candidate for the role of ‘universal memory’ (both nonvolatile and fast), exploits InAs quantum wells and AlSb barriers to create a triple-barrier resonant-tunneling (TBRT) structure. Samsung demonstrates MRAM-based in-memory computing Samsung has demonstrated what it claims is the world’s first MRAM-based in-memory computing. MRAM is considered unfit to standard in-memory computing architectures, as its low resistance prevents the power savings benefits of this processing solution. Samsung have solved this issue by replacing the standard, ‘current sum’ in-memory computing architecture with a new, ‘resistance sum’ architecture. New Intel oneAPI release Intel has recently released oneAPI 2022 toolkits, its unified and cross-architecture programming model for CPUs, GPUs, FPGAs and other accelerators. Innovations include what Intel claims is “the world’s first unified compiler implementing C++, SYCL and Fortran for CPUs and GPUs”, utilizing a common LLVM backend. The new release also introduces various optimizations for AI performance. DAC numbers More than 2,250 badges were picked up at the live DAC 2021 event in San Francisco. A report from the in-person conference has been published by Semiconductor Engineering. Among DAC 2021 presentations, Real Intent has published the Google case study concerning ‘Cloud-Based Static Sign-Off Methodology for TPU Machine Learning Hardware.’ TSMC’s 2022 capex In 2022, TSMC’s capital budget is expected to be between USD 40 billion to USD 44 billion. This is what Wendell Huang, the company’s VP and CFO, told financial analysts during the Q4 2021 earnings call. C. C. Wei, TSMC’s CEO, said that for the full year of 2022 the company forecasts the overall semiconductor market – excluding memory – to grow approximately 9%, while foundry industry growth is forecast to be close to 20%. TSMC is confident it can outperform the foundry revenue growth and grow between mid- to high 20s percent in 2022. C. C. Wei also said that TSMC’s N3 technology development is on track and that it will use the FinFET transistor structure. N3 production at TSMC will start in second half of 2022 and the company expects more new tape-outs for this node during the first year, as compared with N5. Silicon Valley’s startups funding doubled in 2021 According to market intelligence firm CB Insights, Silicon Valley is still, by far, the tech capital of the United States. Startups in the metro area (including San Francisco) raised $105B in 2021, more than doubling 2020’s total of $52B. New York took the second spot at $55B in funding, growing threefold from last year’s $18B. Acquisitions Vishay has signed an agreement to acquire substantially all the assets of Barry Industries (Attleboro, MA) a manufacturer of semiconductor packaging and resistive components. Samtec has acquired Ultra Communications, a manufacturer of high-speed digital and RF fiber optic components, based in Vista, CA. Altair has acquired World Programming, a UK-based technology company specializing in data analytics software. Aptiv has announced a definitive agreement to acquire Wind River from TPG Capital. Nvidia has acquired Bright Computing (Amsterdam, The Netherlands), a company developing software for managing high performance computing systems. SK Hynix has completed the first phase of the transaction to acquire Intel’s NAND and solid-state drive business. The newly established U.S. subsidiary, which will manage the SSD business, will be known as Solidigm ( www.solidigmtechnology.com) and will be headquartered in San Jose, California. Upcoming events ASP-DAC (Asia and South Pacific Design Automation Conference) is running as a fully virtual conference until January 20. Pre-recorded videos will be available until January 28. The European edition of AltiumLive 2022 CONNECT will take place as a virtual event on February 2-4. Semicon Korea will be held on February 9-11. ISSCC (International Solid-State Circuits Conference) will take place as a virtual-only event from February 20 to 28. SPIE Advanced Lithography + Patterning is scheduled as an in-person event from February 27 to March 3 in San Jose, California. MWC Barcelona will run from February 28 to March 3. |

|

|

|||||

|

|

|||||

|

|||||