EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Imperas targets RISC-V verificationDecember 16th, 2021 by Roberto Frazzoli

With its new ImperasDV solution, the company aims at enabling all RISC-V developers to accomplish the complex task of processor IP verification more efficiently “The greatest migration in verification responsibility in the history of EDA,” from processor IP vendors to SoC designers: this, according to Imperas Software, is the challenge facing SoC development teams as they take advantage from RISC-V customization capabilities. One of the reasons for the success of RISC-V is undoubtedly the possibility for any SoC developer of adding some degree of customization to the basic instruction set architecture, while saving the processor compatibility with the RISC-V ecosystem of supporting tools and software. The other side of the coin, however, is a heavier verification burden on the SoC development team: as opposed to an off-the-shelf processor IP which is pre-tested by the vendor, a customized processor needs to be verified by whom performed its customization. Addressing this challenge, Imperas Software has recently launched ImperasDV, an integrated solution for RISC-V processor verification. This new product is the main subject of the video interview that Larry Lapides, Vice-President at Imperas Software, has recently given to EDACafe’s Sanjay Gangal. In this article we will take a closer look at ImperasDV, adding a few details to the video interview content. We will also briefly discuss another major part of Imperas’ product offering, virtual platforms for embedded software development – along with the promotion of open model library availability through the Open Virtual Platforms (OVP) industry consortium. Based near Oxford, UK, with offices in Silicon Valley and Tokyo, Imperas software was founded in 2008 by Simon Davidmann, an EDA veteran.

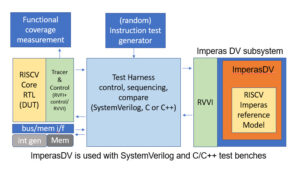

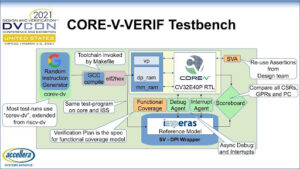

Addressing RISC-V verification with ImperasDV Clearly, the problem with RISC-V verification is that a processor core is the most complex IP block within an SoC: according to Imperas, on average its verification can be 10x the complexity of the SoC that is developed around it. Without a specifically optimized verification solution, this complexity translates in extensive set-up and time-consuming manual adjustments to the established SoC design and verification flow. This is particularly true if custom extensions or modifications are added during the design. Addressing this challenge, Imperas offers SoC developers a ‘reference model-based solution’ that is compatible with the current UVM SystemVerilog methods for SoC verification. “ImperasDV takes what we’ve learned over the last three years in design verification for RISC-V and productizes it,” said Lapides in the video interview. ImperasDV is based on three key components: the Imperas RISC-V golden reference model; integrated test bench components; and test suites. On top of that, the company offers technical support and training. The Imperas RISC-V golden reference model is an ‘envelope model’ that covers the entire RISC-V ISA, including privileged mode. It supports the latest extensions for Crypto (Scalar), Bitmanip, Vector, and DSP/SIMD, as well as user defined custom instructions and extensions. It can also be configured to support previous specification revisions and drafts. As Lapides said in the video interview, Imperas believes that the quality of its processor models is unique as they are extensively tested by a large community of partners and customers. The integrated testbench includes SystemVerilog components compatible with all major EDA environments; C/C++ components for use in C/C++ test benches using Verilator; and a new open standard RVVI (RISC-V Verification Interface). Developed by Imperas in collaboration with customers, RVVI provides integration between RTL, reference model and testbench, and integration for instruction-accurate ‘step-and-compare’ methodology. As the company points out, this methodology can be used to verify an RTL processor implementation against the Imperas golden reference model encapsulated within a SystemVerilog UVM environment. This covers asynchronous events and accelerates transition to debug analysis when an issue is found. The RVVI also supports multi-hart, superscalar and out-of-order CPU pipelines. The integrated testbench enables users to measure verification coverage with instruction level analysis and reporting. Test suites include support for multiple popular ISGs (Instruction Stream Generators), such as the RiscV-DV open source ISG developed by Google or the Force-RiscV open source ISG maintained by the OpenHW Group. Part of the solution, the Valtrix Systems Sting test generator supports pre-integrated Imperas RISC-V reference models to generate portable bare-metal programs containing self-checking architecturally-correct test stimulus. (Valtrix Sting is available with the pre-integrated Imperas RISC-V reference model because of a multi-year distribution and support agreement between the two companies). Other elements included are Imperas Architectural reference test suites (Floating Point, Bitmanip, Crypto, Vector, DSP/SIMD) and RISC-V International architectural compatibility test suites. Step and compare The key concepts behind ImperasDV are also described in a paper by Imperas’ Kevin McDermott, presented at DVCon 2021 and posted on the RISC-V International blog. In particular, the article provides details about the ‘step and compare’ methodology. This approach is enabled by using the same simulation environment for the RTL and reference models – as the Imperas OVP reference model sits inside the SystemVerilog testbench. This single environment approach allows the same debug session to control both the DUT and the reference model. The ‘step-and-compare’ methodology helps identify divergence at the earliest stage and avoids unnecessary simulation cycles. According to Imperas, in other less efficient verification methodologies “post-simulation trace compare would typically keep executing after the first discrepancy, taking more time and resources long after the issue occurred and thus reducing the value of the results beyond the discrepancy event.”  Example of ‘step and compare’ design verification flow. Image credit: DVCon (re-published on the RISC-V International website) The ImperasDV RISC-V processor verification technology is already being used by several companies, including Codasip, EM Microelectronics (Swatch), Nsitexe (Denso), Nvidia Networking (Mellanox), OpenHW Group, MIPS Technology, Seagate Technology, Silicon Labs, and Valtrix Systems. (MIPS has selected Imperas RISC-V reference models as it has started transitioning its processor IP to the RISC-V architecture.) More details on test benches with Imperas RISC-V verification reference models are available at https://www.imperas.com/riscv. The new RVVI (RISC-V Verification Interface) is available at https://github.com/riscv-verification/RVVI. ImperasDV is a commercial product; besides that, the free riscvOVPsimPlus package – including the test suites and instruction coverage analysis, including updates for the latest RISC-V ratified specifications – is available from the OVP website. Virtual platforms for embedded software development The focus on RISC-V simulation is a relatively recent development in Imperas’ activity: since its foundation in 2008, the company is engaged in creating virtual platforms for embedded software development, mainly targeting multi-core SoCs and supporting a wide range of processing architectures. A virtual platform is a software representation of a processor-based system, which includes instruction-accurate processor models coupled with all the peripheral, memory and sub-system models that are required to execute embedded software for functional verification. As Imperas explains, the key to this solution is the availability of ultra-fast software simulation models of processors, peripherals and behavioral components which can execute embedded software up to a billion Instructions per second. As for fast execution performance, Imperas claims that its JIT code-morphing simulation technology allows models of processors, such as the Arm Cortex A-72, to execute at a peak speed of almost 5,000 MIPS, and to boot multi-core Linux in under four seconds on an average desktop PC. As for models, the Imperas OVP library includes a range of processors from Arm, Imagination MIPS, PowerPC, OpenCores, Renesas, Synopsys ARC, Altera Nios II, and Xilinx Microblaze. The models are fully featured, e.g. Arm’s TrustZone and virtualization technology are supported. Platforms and peripherals are also available that run, for example, Linux, Android, Nucleus, μC/OS, FreeRTOS, uClinux, eCos. Models operate with SystemC TLM2 and other standards. The solution includes verification, analysis and profiling tools plus a multi-core debugger using Imperas’ ToolMorphing technology to merge them into the simulator. Tools operate from bare metal instructions to CPU- and OS-Aware abstract modes, and can be customized for platform and scenario specific operations. According to the company, this environment has been used by Imperas’ customers to find bugs in previously fully tested production code. Clearly, the virtual platform approach can also be used to develop embedded software for RISC-V-based SoCs. As explained in the above-mentioned blog post, the same reference model used in the SystemVerilog testbench, in addition to verification, can also be used to execute software early in the project development schedule well before silicon prototypes are available. Virtual platforms VS hardware emulators The concepts behind the virtual platform approach are expressed in more details in the OVP industry consortium website. The basic assumption here is the need to ‘shift left’ embedded software development, with the target to get it up and running very shortly after hardware availability. According to OVP, the most common practice today for developing embedded software is less than ideal: a desktop Windows or Linux development environment is a very different platform from the final target system. Also, a hardware prototype of the system is often unreliable and is often available only near the end of the product development schedule. An alternative is developing software on hardware emulators, but this approach also has drawbacks, according to OVP: “Hardware emulators are often very large and very expensive and are very hard to set up. They suffer from two main problems: a) they require the RTL – which means they are only useful for software development at the very end stages of a chip project, and b) they are very very slow when compared to instruction accurate simulators such as OVPsim or Imperas.” A bit of EDA history Simon Davidmann, founder and CEO of Imperas Software, was one of the original developers of the HILO logic simulation system, and co-authored the definitive book on SystemVerilog. At DVCon 2021 he hosted a personal perspective on the formation and history of SystemVerilog with Phil Moorby, inventor of Verilog HDL and Verilog-XL simulator, and Peter Flake, inventor of HILO and Superlog/SystemVerilog. A key role in this history was played by Co-Design Automation, the company set-up in 1997 by Davidmann and Flake to design and implement a new language and simulator; Moorby joined in 1999. As explained in a press release, “The company name showed the desire to include software/hardware co-design, but there was more customer interest in hardware design and verification, and even system specification. Their original vision of Superlog (derived from Super and Verilog) was to have a single language for system specification, hardware design, hardware verification, and software development. Superlog was later renamed to SystemVerilog as it became adopted by Accellera and later became an IEEE standard.” The evolution of Verilog is the subject of an interesting ninety-page paper authored by Flake, Moorby and Davidmann (with Arturo Salz and Steve Golson) titled ‘Verilog HDL and Its Ancestors and Descendants’. Categories: EDACafe Editorial, Video Interview |

|

|

|||||

|

|

|||||

|

|||||