EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. EDA updates; Indy Autonomous Challenge; Qualcomm-Nuvia deal; RRAM-based edge learning; robomorphic computingJanuary 25th, 2021 by Roberto Frazzoli

Will we see tech students spraying Champagne during the awards ceremony at the Indy Autonomous Challenge next October? What is sure is that the race initiative confirms a strong academic commitment to autonomous vehicle research. Meanwhile, Hyundai Motor and Apple are reportedly planning to sign a partnership deal on autonomous electric cars by March and start production around 2024 in the United States. More about the Indy race below, after some EDA news. Other updates this week concern CPUs, machine learning, and robotics. EDA updates: Ansys, Siemens Ansys has recently launched its new HFSS Mesh Fusion. Available in Ansys HFSS 2021 R1, the new solution enables fully-coupled simulation of entire, complex electromagnetic systems. It combines integrated circuits, packaging, connectors, printed circuit boards, antennas and platform in a single Ansys HFSS analysis to predict electromagnetic interactions. The EDA business of Siemens – formerly Mentor – has announced that its tools for the verification of analog/mixed-signal circuits are now qualified for early design starts on Samsung Foundry’s new 3nm Gate All Around process technology. Early-stage AMS designs can now be verified using the Analog FastSpice (AFS) platform on Samsung’s most advanced process technology.

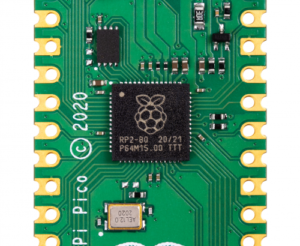

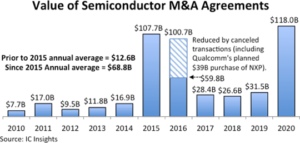

The Indy Autonomous Challenge Next October 23rd the Indianapolis Motor Speedway will host the first Indy Autonomous Challenge (IAC), with the participation of twenty-eight teams representing thirty-nine university from around the world. Teams will not be asked to develop and produce any hardware components; the focus is on developing new generations of software for autonomous vehicles. Common to all teams will be the same official racecar, recently unveiled at the CES: a modified Dallara IL-15, described as “the most advanced, fastest autonomous vehicle ever developed”.  No driver’s seat. The Dallara racecar selected for the Indy Autonomous Challenge. Credit: Indy Autonomous Challenge The Dallara IL-15 racecar has been retrofitted with hardware and controls by Clemson University (Clemson, South Carolina) to enable automation. Clemson’s students are also tasked with determining the sensor types and locations to provide the vehicle with computer vision at high speeds, considering their influence on the aerodynamics of the vehicle. A qualifying simulation race will be held during the Indy 500 week in May. The total prize purse is $1.5 million: $1 million awarded to the winning team in October, and an additional $500,000 for winners of hackathons and simulation races, awarded by IAC sponsor, Ansys. Ansys will also play a key role by providing teams with a simulation platform based upon its VRxperience Driving Simulator, powered by SCANeR, along with its Scade software development suites. Qualcomm adds prestigious CPU design team through the acquisition of Nuvia Catching up on last week’s news, a comment about Qualcomm’s acquisition of CPU startup Nuvia deserves attention. Analyst Patrick Moorhead describes the deal as a strategically important move for Qualcomm – mostly because of the experience and talent of the Nuvia team, which includes John Bruno, Gerard Williams and Manu Gulati. Nuvia was founded in early 2019 with the declared goal of “reimagining silicon design to deliver industry-leading performance and energy efficiency for the data center.” Moorhead expects Qualcomm “to retarget Nuvia’s IP to the smartphone and PC versus getting into the general-purpose server CPU market.” RRAM-based edge learning French research institute CEA-Leti claims to have achieved a machine-learning breakthrough that opens way to learning at the edge, exploiting what have been previously considered as “non-ideal” traits of resistive-RAM (RRAM) devices. RRAM are a promising candidate for the implementation of neural networks using in-memory computation, to drastically reduce energy requirements. However, RRAM randomness is not a good fit for the commonly used training algorithm – backpropagation – which requires high-precision memory elements. To get around that problem, the team developed a method that actively exploits that memristor randomness, implementing a special sampling learning algorithm (a Markov Chain Monte Carlo) in a fabricated chip that acts as a Bayesian machine-learning model. The work has been reported in a paper published on the January issue of Nature Electronics. Robomorphic computing: robot-specific hardware acceleration ‘Robomorphic computing’ is the expression coined by a group of researchers from MIT and Harvard University who has come up with the concept of designing customized accelerator chips to minimize robots’ response time. The proposed design methodology aims at transforming robot morphology into customized accelerator hardware morphology by exploiting robot features such as limb topology and joint type. A key idea here is that a robot’s physical structure (its limbs and joints) imposes a series of constraints to its movements: many movements are just impossible, and this means that the problem of driving a robot’s motion involves a high level of ‘sparsity’. So far, the researchers have tested their ideas using an FPGA, achieving significantly higher performance compared to a standard CPU or GPU. Here is an extended abstract of the work, which will be presented at this April’s ASPLOS Conference (International Conference on Architectural Support for Programming Languages and Operating Systems). A Raspeberry MCU The Raspberry Pi organization has just announced its own silicon: a microcontroller called RP2040. Based on a dual-core Arm Cortex-M0+ running at 133MHz, it integrates 264KB of on-chip RAM and is fabricated in a 40-nanometer process. Its two square millimeters die is contained in a 7 × 7 mm QFN-56 package. The MCU is available on the new Raspberry Pi Pico board, on sale at $4. More acquisitions Cadence has entered into a definitive agreement to acquire Belgium-based Numeca, a provider of computational fluid dynamics (CFD), mesh generation, multi-physics simulation and optimization solutions. Numeca’s products are used in many industries including aerospace, automotive and marine, by customers such as NASA, ArianeGroup, Honda and Ford. Numeca’s CFD technology complements Cadence’s finite element analysis technologies, addressing areas such as internal and external flows, acoustics, heat transfer, fluid-structure interaction and optimization. Silvaco has completed the acquisition of physical verification solution and cloud enablement provider Polyteda Cloud, based in Ukraine. The acquisition is aimed at expanding Silvaco’s capabilities for rapid physical verification of IC designs prior to mask creation and manufacturing, and for cloud enablement of EDA tools. And according to market research firm IC Insights, the total value of M&A agreements in 2020 amounted to an all-time high of $118.0 billion, surpassing the previous record of $107.7 billion reached in 2015. Most part of this figure – about 80% – was made up by just five big deals. |

|

|

|||||

|

|

|||||

|

|||||