EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Major stories this week: DAC news; AI edge processors; ML advancements; automotive; 5G; market data; acquisitionsJune 6th, 2019 by Roberto Frazzoli

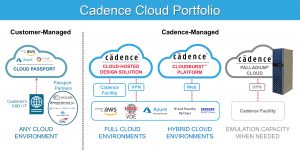

PCI Express 5.0 is here: recently announced specification confirms the expected 32GT/s transfer rates while maintaining low power and backwards compatibility with previous PCI generations. Many more news are coming from different areas as usual, but – with DAC just ended – EDA announcements abound this week. DAC itself is making news, preannouncing that it will co-locate with SEMICON West in July 2020 and July 2021. Events will take place at the Moscone Convention Center in San Francisco. Cadence news Cadence has launched its new Cloud Passport Partner Program to give customers an easier path to the cloud when their internal IT teams desire assistance. Customers now have the option to get support from Cadence-authorized cloud enablement providers. Inaugural members include Rescale, Scala Computing and Nimbis Services, as well as academic partners CMC Microsystems and Europractice. Cadence has also announced the Spectre X Simulator, a massively parallel circuit simulator providing up to 10X performance gains, while maintaining the same accuracy of previous Spectre generations. The new tool can solve 5X larger designs, enabling simulation of circuits containing millions of transistors and billions of parasitics in a post-layout verification flow.

Synopsys news Synopsys has collaborated with Globalfoundries to develop a portfolio of DesignWare IP for GF's 12LP (12nm) FinFET process technology, including multi-protocol 25G, USB 3.0 and 2.0, PCI Express 2.0, DDR4, LPDDR4/4X, MIPI D-PHY, SD-eMMC, and data converters. Synopsys is also launching a new release of its Verification Continuum Platform with new native integrations across verification tools, enabling up to 5X higher verification performance. And the Synopsys Fusion Design Platform has been certified for Samsung's 5nm Low-Power Early (LPE) process with EUV lithography technology. More DAC-related news AMD engineers have executed a physical verification pass of the Radeon Instinct Vega20 – a 7nm chip design with 13.2B transistors – in ~10 hours using the TSMC-certified Calibre nmDRC software platform from Mentor, running on the Microsoft Azure cloud platform using HB-series virtual machines, powered by AMD EPYC processors. French research institute Leti and Silvaco have announced a project to estimate and model the yield of ultra-low-voltage, ultra-low-leakage SRAM. The initiative will employ Silvaco’s VarMan eXtreme Memory Analysis (XMA) tool. Against current assumptions used in industry about yield and variability, evidence of non-Gaussian margin distribution in some cases has been found with the help of Silvaco VarMan. Open-source EDA resources Silvaco has provided an open-source, 15nm standard-cell library to Silicon Integration Initiative, an EDA software R&D joint venture. Efabless will add Globalfoundries’ 130nm process technology (130G) to its crowdsourcing design platform for custom silicon. Efabless provides a complete EDA design flow based on open-source tools and other capabilities, to develop custom ICs and silicon-proven IP with limited costs and resources. AI edge processors International Data Corporation (IDC) estimates that worldwide shipments of AI-optimized processors for edge systems will reach 340.1 million units in 2019, an increase of 170% over 2018. By 2023, IDC expects the market will reach unit shipments of 1.5 billion and achieve a five-year CAGR of 64.9%. In 2018, only 5.1% of edge systems running AI included optimized processors. According to the IDC forecast, this penetration rate will reach 40.5% by 2023, while revenues for AI-optimized processors on the edge will touch $40.4billion by 2023, with a CAGR of 86.4%. Among the companies targeting this growing market is BrainChip, whose Akida Neural Processing Core is now available for licensing as an IP block for incorporation into ASICs. The core is based on neuromorphic circuits using an event-based spiking neural network technology. Helping the machine learning community Google is releasing TensorNetwork, a new open source library to improve the efficiency of tensor calculations, developed in collaboration with the Perimeter Institute for Theoretical Physics and X. TensorNetwork uses TensorFlow as a backend and is optimized for GPU processing. The initiative aims at facilitating the widespread use of tensor networks in the machine learning community by removing two difficulties: 1) the lack of a production-level tensor network library for accelerated hardware to run tensor network algorithms at scale, and 2) the false impression that understating tensors requires expertise in quantum mechanics. Apple, on its part, is facilitating machine learning apps: among the many announcements from the Apple WWDC19 event, the company unveiled updates to Core ML and Create ML, that allow for more powerful and streamlined on-device machine learning apps – for vision, natural language and speech. Automotive standards At the TU-Automotive Detroit show (June 5-6 in Novi, Michigan), the Israeli company Autotalks in collaboration with Marben conducted a live V2X demo based on Marben V2X software solution running on Autotalks’ chipset. The joint demonstration showed V2V applications using both DSRC and C-V2X standards, and leveraged the ability of the Autotalks’ chipset to support both. At the same event, Valens – another Israeli company – announced that the MIPI Alliance has selected its technology as the baseline for Profile 2 of the A-PHY physical layer standard, which will provide high-speed links (up to 48Gbps and above) for cameras, displays and sensors within a vehicle. Smartphones and 5G AMD has announced that custom graphics IP based on the Radeon RDNA architecture will be licensed to Samsung for use in mobile devices, including smartphones. And pSemi (formerly Peregrine Semiconductor), a Murata company, has released UltraCMOS 13, the new generation of its proprietary RFSOI technology (silicon-on-insulator for RF applications), manufactured in high-volume 300mm foundries. Claiming excellent RONCOFF and FMAX performance, the new technology will initially target 5G-NR sub-6GHz applications, including low-noise amplifiers, power amplifiers and switches. Acquisitions: Infineon-Cypress, Dialog-FCI Infineon will acquire Cypress for US$23.85 per share in cash, corresponding to an enterprise value of €9.0 billion. Cypress’ microcontrollers and connectivity components will be combined with Infineon's power semiconductors, sensors and security solutions, targeting applications such as electric drives, battery-powered devices, power supplies, IoT, and automotive. With this move Infineon also adds to its R&D resources in Silicon Valley and gains presence in the Japanese market. Dialog Semiconductor has acquired the mobile communications product line of Silicon Motion, called FCI. FCI products include 2G/3G/4G transceivers as well as SoCs for ultra-low power Wi-Fi, mobile TV, and electronic toll collection.  First Wi-Fi product from Dialog following the acquisition of FCI product line. Image credit: Dialog Semiconductor SIA and SEMI market data The Semiconductor Industry Association (SIA) has announced that worldwide sales of semiconductors were $32.1 billion in April 2019, a decrease of 14.6 percent from the April 2018 total of $37.6 billion and 0.4 percent less than the March 2019 total of $32.3billion. Annual global sales are forecasted to decrease 12.1 percent in 2019, then increase 5.4 percent in 2020. SEMI has reported that worldwide semiconductor manufacturing equipment billings for the first quarter of 2019 dropped 8 percent from the previous quarter and 19 percent from the same quarter in 2018 to US$13.8 billion. Category: EDACafe Editorial |

|

|

|||||

|

|

|||||

|

|||||