EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Major stories this week: smartphone shakeup; FPGAs; analog IP; UVM; SLAM; acquisitions; smart buildingsMay 24th, 2019 by Roberto Frazzoli

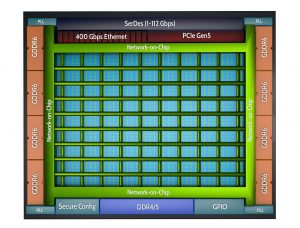

Just a brief mention of recent news that have been thoroughly covered by all types of media – including dinnertime TV newscast. Following Google’s decision to blocks Huawei access to Android updates after blacklisting, the Chinese company has reportedly preannounced its own new operating system for its smartphones. ARM, too, is reportedly “complying with the latest restrictions set forth by the U.S. government”. A totally unrelated fact is adding to this scenario: the court ruling that Qualcomm’s licensing practices relating to its modem chips constitute an unfair method of competition. All these stories are still evolving, but a shakeup in the smartphone-related ecosystem seems to be unavoidable. New FPGAs target AI applications, firmware security Though not popular enough for prime time, FPGAs are also making news with innovations from Achronix and Lattice. Achronix has introduced the Speedster7t FPGA family, based on a new architecture optimized for artificial intelligence/machine learning and data acceleration applications. At the heart of Speedster7t FPGAs are a massively parallel array of programmable compute elements within the new machine learning processors (MLPs). The MLPs support integer formats from 4 to 24 bits and floating-point modes including direct support for TensorFlow's 16-bit format. Tightly coupled with embedded memory blocks, the MLPs are fed with data at 750 MHz. The Speedster7t architecture includes a two-dimensional network-on-chip that spans horizontally and vertically over the FPGA fabric. Each row or column in the NoC is implemented as two 256-bit, unidirectional AXI channels operating at 2 GHz, delivering 512 Gbps of data traffic in each direction simultaneously. Other features include up to 72 SerDes that can operate from 1 to 112 Gbps, 400G Ethernet ports, PCI Express Gen5 controllers, and GDDR6 interfaces. Manufactured on TSMC's 7nm FinFET process, Speedster7t devices range from 363K to 2.6M 6-input LUTs and offer a conversion path to ASIC.

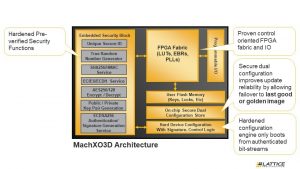

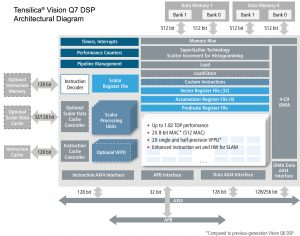

Lattice has announced the MachXO3D FPGA for protecting systems against a variety of firmware-related threats, by securing communication between the FPGA itself and legitimate firmware providers. This protection stays in effect throughout the component’s entire lifecycle, including system manufacture, transit, installation, operation and decommissioning. Security features include an embedded block that provides pre-verified hardware support for cryptographic functions such as ECC, AES, SHA, PKC and Unique Secure ID; an embedded secure configuration engine to ensure only FPGA configurations from a trusted source can be installed; dual on-device configuration memories to enable fail-safe reprogramming of component firmware in the event of compromise. According to Lattice, this is the first control-oriented FPGA compliant with NIST’s Platform Firmware Resilience specification. AI-driven analog design pioneer gets new funding Investors are showing confidence in Agile Analog, a Cambridge (UK) analog IP company that has developed an AI-driven platform to replace the existing manual analog design process. The latest Pre-A funding round includes Delin Ventures, firstminute Capital and MMC Ventures, totalling $5M. In Agile Analog’s view, automating analog design is not only a way to improve productivity; rather, automation should allow customers to incorporate more analog onto their chips and significantly reduce the size and cost of end products. Agile Analog aims to enable a departure from the current technology mix, where simple analog portions of the design must be compensated by complex digital portions. Automatic UVM code generation DAC announcements start pouring in. Agnisys will introduce its Specta-AV UVM Testbench Generator aiming to automate code generation for Accellera’s Universal Verification Methodology. According to Agnisys, power-users of UVM still have to manually write a massive amount of code in the range of multi-millions. “UVM has reached maturity and is now ready for a fully-automated tool flow,” stated Anupam Bakshi, Agnisys founder and CEO, in a press release. “With the current version of Specta-AV, we’re able to generate about 50-60% of the required UVM code to verify a full SoC (…). We will continue to build it to reach our vision where 100% of the required UVM code is automatically generated.” SLAM-optimized solutions from both Cadence and Synopsys DAC themes will also include vision-related functions such as Simultaneous Localization And Mapping (SLAM), the computational problem of constructing or updating a map of an unknown environment while simultaneously keeping track of an agent's location within it. Cadence has introduced of the Tensilica Vision Q7 DSP delivering up to 1.82 tera operations per second (TOPS), targeting demanding edge vision applications and specifically optimized for SLAM. Synopsys and Kudan, a SLAM software algorithms licensor, have announced a collaboration to optimize Kudan's SLAM computer software algorithms for Synopsys' DesignWare ARC EV6x Embedded Vision Processor IP. SLAM is used in autonomous vehicles, drones, robots, and augmented reality applications. Acquisitions: Marvell-Avera, HPE-Cray Marvell will purchase Avera Semiconductor, the ASIC business of Globalfoundries. Marvell is focused on becoming the world's leading supplier of semiconductor solutions for wired and wireless infrastructure; the addition of Avera – previously part of IBM's Microelectronics business – enables Marvell to offer a larger spectrum of product architectures spanning standard, semi-custom to full ASIC solutions. Initial targets of the combined companies include the 5G base station market. Hewlett Packard Enterprise will acquire supercomputer manufacturer Cray in a transaction valued at approximately $1.3 billion. The addition of Cray strengthens and expands HPE’s High Performance computing portfolio, currently including HPE Apollo and SGI. Smart home chips, PoE lighting At the recent Connections Conference in San Francisco, Redpine Signals announced a new chip for smart home devices featuring multiple wireless protocols and low power consumption. The RS9116N-DBT integrates an ARM Cortex M4 MCU, advanced hardware security, and protocols stacks for Wi-Fi, BT, BLE, ZigBee and Thread. It consumes less than 113uA for maintaining cloud connection over Wi-Fi. In enterprise connected lighting applications, Power over Ethernet is gaining traction with the new IEEE 802.3bt standard providing more power. Microchip – via its Microsemi subsidiary – has announced an eight-port PoE switch compliant to the new standard, that provides 60 watts per port for all eight ports simultaneously. Category: EDACafe Editorial |

|

|

|||||

|

|

|||||

|

|||||