Just a brief mention of recent news that have been thoroughly covered by all types of media – including dinnertime TV newscast. Following Google’s decision to blocks Huawei access to Android updates after blacklisting, the Chinese company has reportedly preannounced its own new operating system for its smartphones. ARM, too, is reportedly “complying with the latest restrictions set forth by the U.S. government”. A totally unrelated fact is adding to this scenario: the court ruling that Qualcomm’s licensing practices relating to its modem chips constitute an unfair method of competition. All these stories are still evolving, but a shakeup in the smartphone-related ecosystem seems to be unavoidable.

New FPGAs target AI applications, firmware security

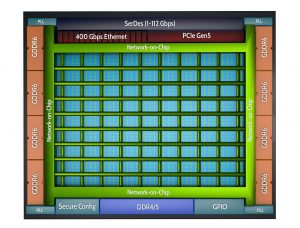

Though not popular enough for prime time, FPGAs are also making news with innovations from Achronix and Lattice. Achronix has introduced the Speedster7t FPGA family, based on a new architecture optimized for artificial intelligence/machine learning and data acceleration applications. At the heart of Speedster7t FPGAs are a massively parallel array of programmable compute elements within the new machine learning processors (MLPs). The MLPs support integer formats from 4 to 24 bits and floating-point modes including direct support for TensorFlow's 16-bit format. Tightly coupled with embedded memory blocks, the MLPs are fed with data at 750 MHz. The Speedster7t architecture includes a two-dimensional network-on-chip that spans horizontally and vertically over the FPGA fabric. Each row or column in the NoC is implemented as two 256-bit, unidirectional AXI channels operating at 2 GHz, delivering 512 Gbps of data traffic in each direction simultaneously. Other features include up to 72 SerDes that can operate from 1 to 112 Gbps, 400G Ethernet ports, PCI Express Gen5 controllers, and GDDR6 interfaces. Manufactured on TSMC's 7nm FinFET process, Speedster7t devices range from 363K to 2.6M 6-input LUTs and offer a conversion path to ASIC.