Archive for January, 2022

Tuesday, January 25th, 2022

In my recurring blog post series for SEMI, I interviewed Michiel Ligthart, president and COO. Here’s the Q&A as it appeared on the SEMI website in October.

Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification. Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification.

I spoke with Verific president and COO Michiel Ligthart about homegrown and open-source EDA tools and other recent trends in chip design.

Smith: What trends are you seeing in chip design?

Ligthart: Semiconductor companies are starting to build a portfolio of intellectual property, including homegrown electronic design automation (EDA) tools, that they want to keep secure and differentiated from their competitors. The increased interest in internally developed and supported EDA tools is a trend we started to see about two years ago. It’s not simulation, synthesis or place and route (P&R). Instead, it’s pieces of a chip design flow optimized for a company’s specific needs.

In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example. In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.

Is this a widespread trend? It could be. We hear about it within end-user applications ranging from 5G and AI to data center processors and there are probably others we don’t hear about. Power optimization is an example of the kind of specific internal need being addressed.

(more…)

No Comments »

Sunday, January 16th, 2022

Let’s cheer for a piece of great news –– the Electronic System Design industry revenue increased 17.1% year-over-year from $2,953.9 million to $3,458.1 million in Q3 2021! This comes from the most recent Electronic Design Market Data (EDMD) report produced by the ESD Alliance, a SEMI Technology Community, where I serve as Executive Director.

The four-quarter moving average comparing the most recent four quarters to the prior four rose 16.1%. All regions reported double-digit growth with product categories CAE, Printed Circuit Board and Multi-Chip Module, semiconductor IP and Services showing double-digit growth.

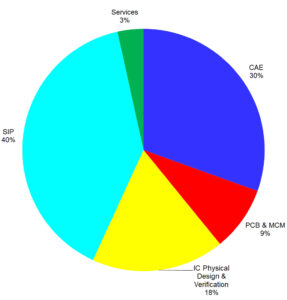

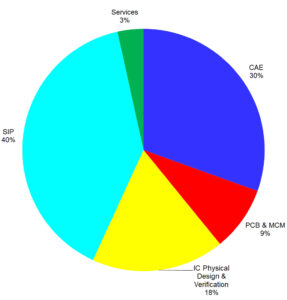

Q3 2021 revenue percentage by category Taking a deeper dive into the year-over-year revenue by product and application category shows:

- CAE revenue increased 13.7% to $1,054.7 million and the four-quarter moving average increased 11.8%.

- IC Physical Design and Verification revenue rose 0.7% to $612.6 million with the four-quarter moving average of 16% growth.

- Printed Circuit Board and Multi-Chip Module (PCB and MCM) revenue increased 14.5% to $298.3 million. The four-quarter moving average saw an increase of 10.9%.

- Semiconductor IP revenue rose 30.6% to $1,373.3 million for a four-quarter moving average of 22.1% growth.

- Services revenue increased 12.5% to $119.1 million. The four-quarter moving average increased 9.2%.

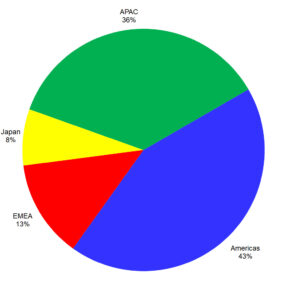

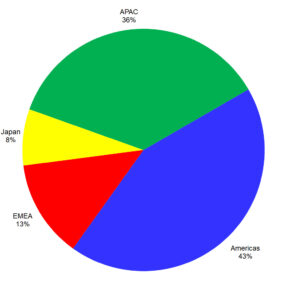

Q3 20201 revenue percentage by region As for the year-over-year revenue change by region:

- The largest reporting region by revenue is the Americas. The region purchased $1,494.5 million of ESD products and services in Q3 2021, a 14.3% increase. The four-quarter moving average rose 15.8%.

- Europe, Middle East, and Africa (EMEA) revenue increased 22.6% to $451.7 million with a four-quarter moving average of 11.9% growth.

- Japan revenue increased 11.8% to $259.8 million and the four-quarter moving average rose 3.3%.

- Asia Pacific (APAC) revenue increased 19.7% to $1,252.1 million. The four-quarter moving average grew by 21.3%.

Significantly, companies tracked in the EDMD report employed 51,182 people globally in Q3 2021, an 8.7% increase over the Q3 2020 headcount of 47,087 and up 2.4% compared to Q2 2021.

The ESD Alliance Electronic Design Market Data (EDMD), formerly known as the Market Statistics Service, report has much more detailed information than provided here. Published quarterly, it presents EDA, SIP and services industry revenue data from public and private companies. Each quarterly report is published approximately three months after quarter close.

(more…)

No Comments »

Monday, January 10th, 2022

I originally wrote an article drawing comparisons between chip design and manufacturing and winemaking back in 2009. While a lot has changed since then, especially in the semiconductor and electronics industry, many of the comparisons still hold true. I originally wrote an article drawing comparisons between chip design and manufacturing and winemaking back in 2009. While a lot has changed since then, especially in the semiconductor and electronics industry, many of the comparisons still hold true.

From a high-level view, what do chip design and manufacturing have in common with winemaking?

It turns out that, in both cases, it’s all about the process. Although I have spent much of my career in the semiconductor, EDA and IP industries, I have had the opportunity to participate in a small, commercial winemaking venture called Jazz Cellars for the past 16 years. It might sound like a stretch (so bear with me) but I think there are some interesting parallels and a few significant differences between the processes involved in producing wine and semiconductor chips.

One shared characteristic of both chip design and winemaking is that there is no instant gratification –– it takes time and effort to yield a great end product. While it may be possible to turnaround a simple chip design in a few months, most complex designs often take years to go from concept to market. The same is true for a wine –– many red wines are not released until three or more years after the grapes were initially harvested. There are exceptions of course such as Beaujolais Nouveau, always released on the third Thursday of November, and some white wines that may be released just a few months after they are harvested. One shared characteristic of both chip design and winemaking is that there is no instant gratification –– it takes time and effort to yield a great end product. While it may be possible to turnaround a simple chip design in a few months, most complex designs often take years to go from concept to market. The same is true for a wine –– many red wines are not released until three or more years after the grapes were initially harvested. There are exceptions of course such as Beaujolais Nouveau, always released on the third Thursday of November, and some white wines that may be released just a few months after they are harvested.

Let’s look at some of the similarities between the processes involved in winemaking and chip design. For the sake of discussion, I am assuming a generalized, high-level description of the processes involved.

Both processes start with an initial plan. For the chip, the plan is the system design and global specifications for the chip –– its functional spec, operating speed, power consumption, target process technology, interface, package type, and the like. In winemaking, the plan describes what type of finished wine we are trying to achieve. This includes the varietal of grape and the profile of the finished wine. For example, we may decide to make an aggressive red wine with a strong tannin profile that will age for a long time or we may decide that we want to make a soft, fruit-forward wine that will be easily drinkable early on.

(more…)

No Comments »

Tuesday, January 4th, 2022

Note: Here’s another Q&A post I did for the SEMI blog. In this interview, I talk with John Lee, Rich Goldman and Marc Swinnen of Ansys.

Spend any time with Ansys’ John Lee, Rich Goldman or Marc Swinnen and you’ll hear plenty of optimism about the semiconductor industry even though they tick off a long list of looming design challenges. The need for reliable and effective electronic systems, they emphasize, is great and runs through high tech, aerospace and defense, automotive, IoT and 5G with communications being a common denominator.

The three are especially bullish these days on changing market dynamics brought on by systems companies building company-specific bespoke, or custom, silicon. These systems companies are building chips with a different perspective and a fresh look at silicon design, a move away from the more traditional segment-specific silicon due to much more complexity.

Ansys, a member of the ESD Alliance, a SEMI Technology Community, is a 4,100-employee company with a comprehensive portfolio of multiphysics engineering simulation software for product design, testing and operation products and services. John, Rich, Marc and I focused on Ansys’ semiconductor and electronics segment for our conversation.

(more…)

No Comments »

|

Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification.

Alameda, Calif.-based Verific Design Automation, a member of the ESD Alliance, made its name in the electronic system design and semiconductor industry supporting companies ranging from startups to billion-dollar industry leaders such as Synopsys, Cadence, Siemens EDA, Xilinx, Microchip, NVidia, Infineon, Qualcomm, Renesas and Samsung. Its software is used as the front end to design automation tools such as synthesis, simulation, debug, and formal verification. In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.

In the past, a semiconductor company would either standardize on one EDA company’s chip design flow or mix and match best-in-class tools from different vendors. The common denominator was that they used off-the-shelf products. If they had a specific requirement, they went to the EDA provider for assistance. In today’s competitive landscape, semiconductor companies are figuring out ways to diversify themselves and their design flow became a way to do so. They may not build their own P&R tool, but they will look at building their own power domain approach, for example.