Arteris IP Blog arterisip

Automating System-on-Chip Integration for the 21st CenturyJuly 19th, 2023 by arterisip

By Pascal Chauvet Today’s multi-billion-transistor system-on-chip (SoC) devices are composed of hundreds of functional intellectual property (IP) blocks. The creation of SoCs is typically a combination of acquired IP blocks from trusted third-party vendors and a few internally developed IP blocks containing the secret sauce that differentiates the design from competitive offerings. Third-party IPs may include central processing units, graphics processing units, memory subsystems, dynamic memory access controllers, external memory controllers and communications functions such as Ethernet, USB and MIPI. Internally developed IPs may include hardware accelerators and machine learning inference engines. The different IP blocks must be carefully integrated for the device to work properly. SoC integration is the process of gathering all of these IPs together to form a complete device, but this involves much more than simply plugging them into each other like the pieces of a jigsaw puzzle. SoC integration is challenging, involves hidden complexity and is prone to errors. Designers consistently integrate diverse content from multiple sources while collaborating with teams across various sites with limited cross-team synergy. A large variety of their tasks necessitates a significant amount of manual operations. Because of these challenges, designs are delayed and schedules slip, leading to missed time-to-market and time-to-revenue goals.

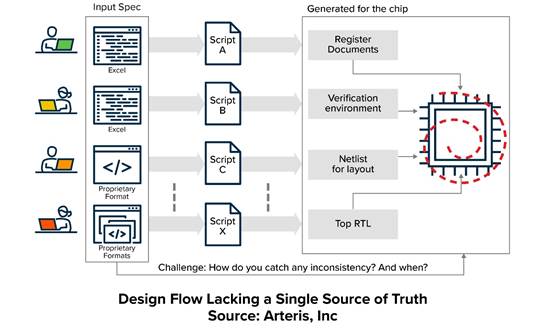

Managing Metadata by Hand The term metadata means data about data. It summarizes the basic information about the data that can make tracking and working with specific data easier. Each IP is described by a comprehensive set of associated metadata. For example, the bits that form its input and output ports, the communication protocols it uses, any reset and interrupt signals, the size and address spaces of any memory it contains, and details about any control and status registers (CSRs). This information includes their addresses and which bits can be read from or written to. Metadata manifests itself in many forms. In the early days of SoC design, metadata was stored in data sheets or spreadsheets created and maintained by hand. A typical design environment and flow would involve multiple teams working in parallel, each with their own internally developed scripts, tools and, often, file formats.

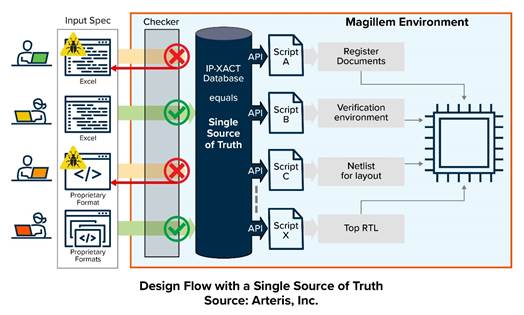

Figure 1. Design teams create and input their own files, lacking single source of truth resulting in costly interations. In such a scenario with no single source of truth, as illustrated in Figure 1, each team would create and maintain its own input files, very often containing overlapping information. However, this data was often not fully aligned or became misaligned when one team made design decisions that were not fully communicated to the other teams. A classic example would be hardware designers modifying CSR names, addresses and functionalities without communicating these changes to the embedded software development team, who were busy writing firmware and device drivers. In this case, problems might only appear during the hardware and software integration phase deep in the product development cycle. Managing Metadata with IP-XACT Originally created in the early 2000s, IP-XACT is a metadata format developed from the ground up to facilitate the management and integration of SoC IPs. The latest version was published in 2022. IP-XACT resulted in a rich standard that addresses the packaging of IPs. It also contains additional constructs to handle corner cases, supports the use of automation and facilitates the creation of automated design flows. It’s important to understand that IP-XACT only provides for specifying and storing metadata associated with an IP. It is a machine-readable format intended to be generated and consumed by machines, not people. To take full advantage of IP-XACT, it is necessary to have corresponding tools and an appropriate development environment. Many companies have opted to develop their own homegrown tools and infrastructure. The scripts often become a collection of various languages, such as Tcl, Perl and Python. It is easy to end up with environments that include hundreds of thousands of lines of code that no one knows how to maintain because it was developed over time by many contributors. Another scenario is startup companies that cannot support a large CAD team. Often, they will scavenge poor-quality freeware tools and stitch something together. As a result, they may spend valuable engineering time detecting and fixing bugs that were introduced because the freeware tools are not validated and are largely unsupported. Managing Metadata with IP-XACT and Magillem The best solution is the Magillem environment tool from Arteris. The product provides a toolbox that allows companies to build their own automation infrastructure and develop their own CAD environment to facilitate SoC integration. The tool provides a development flow based on a single source of truth, as illustrated in Figure 2.

Figure 2. The efficient development flow leveraging Magillem from Arteris. Consider an extremely simple scenario involving only ten IPs, nine procured from third-party vendors and the tenth developed in-house. When the nine acquired IPs arrive, only seven are delivered with corresponding IP-XACT models. The other two arrive with only a subset of IP-XACT models. The in-house developed IP must still have the IP-XACT model created. Fortunately, the Magillem tool is able to integrate all ten IPs. The tool can automatically aggregate component information from different sources to verify their semantic and syntactic correctness. It will merge them into a single structured and standard-based format for several design tasks and teams, avoiding any inconsistency. How Magillem Automation Integrates SoCs With IP-XACT The tool defines the design hierarchy for stitching all the IPs together. This process is more than simply connecting port A on IP #1 to Port B on IP #2, which is not trivial. It involves configuring and instantiating each IP, recognizing port types AXI and OCP, creating interfaces and building each IP into the hierarchy. An important consideration is the underlying interconnect fabric. Large SoC designers have developed their own fabric over many years and may prefer to continue utilizing it. In this context, the Magillem environment is fabric agnostic, allowing users to package their preferred fabric into the tool and automate the process. Additionally, the tool seamlessly integrates with Arteris’ industry-leading NoC IPs, including the FlexNoc 5 interconnect IP and its cache-coherent Ncore interconnect IP. The output is a hierarchical RTL netlist of the entire design and other collateral data. This encompasses makefile scripts for an extensive range of EDA tools and connectivity reports that bring clear visibility to integration status. The Magillem environment makes it easy to rearrange the hierarchy, including upgrading individual IPs and restructuring the design in a way that can be automatically communicated to the downstream physical layout team. The Magillem tool provides a single source of truth, ensuring synchronization between hardware (HW), software (SW) and the documentation database. It enables straightforward register information capture with automatic import of the golden reference memory map into IP-XACT. Additionally, it provides comprehensive consistency checks and creates error-free RTL register banks, UVM verification templates, documentation and software headers from system map information down to the bitfield level. Indeed with full integration of connectivity and register management, the Magillem tool is able to generate and validate the system address map and all the HW/SW interface collateral. The process of assembling an SoC becomes challenging whenever there are different versions of an IP or a new requirement that may break the build flow. It is essential to have tools, data models and an environment that can quickly and safely adapt to these changes, reducing the effort regarding tedious and error-prone tasks. By using Magillem, these capabilities can be fully automated and employed in a continuous integration pipeline. Arteris has deep expertise and broad experience perfecting these features, guiding design teams and empowering them to improve their productivity and achieve first time right projects. Summary Arteris offers three products that facilitate SoC integration automation: Magillem Connectivity, which accelerates the design of complex systems; Magillem Registers, which automatically builds error-free system memory maps; and the CSRCompiler, which streamlines the creation of hardware-software interfaces. These Arteris products radically improve the design process making it easier, faster and less risky. Design teams can leverage these tools to maximize their productivity and expertise. To learn more about SoC integration automation from Arteris, click here. About Author: Pascal leads sales and engineering support activities for SoC integration products at Arteris. Before Arteris, Pascal held senior roles in sales, technical marketing and engineering at Magillem, Sonics, CoWare and STMicroelectronics, gaining extensive experience in semiconductors, EDA, system-level design and semiconductor IP. He has a BSEE from École Supérieure d’Ingénieurs en Électrotechnique et Électronique (ESIEE Paris) and a MSEE from Conservatoire National des Arts et Métiers (CNAM). |

|

|

|||||

|

|

|||||

|

|||||