Arteris IP Blog Frank Schirrmeister

Frank Schirrmeister is vice president of solutions and business development at Arteris. He leads activities in the automotive, data center, 5G/6G communications, mobile, aerospace and data center industry verticals and the technology horizontals artificial intelligence, machine learning and safety. … More » Arteris and Arm Put the Pedal to the MetalOctober 20th, 2022 by Frank Schirrmeister

The pace of change is picking up in the automotive industry. Three areas of innovation are converging. The first is the trend toward electric vehicles (EVs). The second is the increasing sophistication of advanced driver-assistance systems (ADAS) combined with ever greater levels of autonomy. The third is referred to as the “digital cockpit,” which—broadly speaking—refers to the digital experience within the car, including instrument clusters, multi-screen displays, heads-up displays, advanced navigation systems, infotainment systems, voice assistants and the list goes on. All of this is leading to the concept of software-defined vehicles (SDVs), whose features and functions are primarily enabled through software with updates and new services being delivered over-the-air (OTA). SDVs offer significant safety and convenience features and enable new in-vehicle experiences and functions.

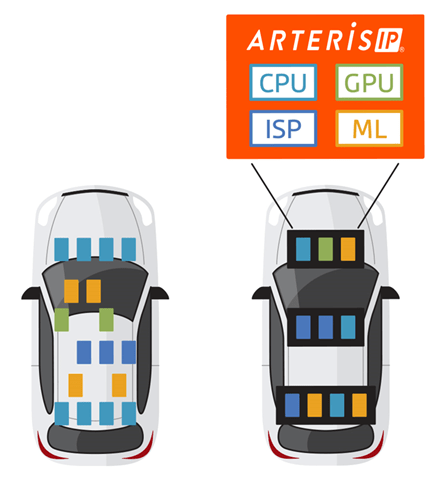

Figure 1. Addressing the compute challenge of the software-defined vehicle requires compelling SoCs, which—in turn—require integrated IP solutions. Of course, software requires processing platforms to run on, and today’s vehicles boast vastly more computing power than was provided by early supercomputers. Addressing the compute challenges of SDVs requires the development of compelling system-on-chip (SoC) devices featuring energy-efficient and cost-competitive heterogeneous compute cores. In turn, developing these SoCs requires integrated IP solutions, including hardware (both processors and interconnect), software and verification IP. Evolving Automotive Compute Architectures Automotive compute architectures are constantly evolving. Early systems featured multiple automotive microcontroller units (MCUs), each focused on a particular task. Over time, this transitioned to zonal controllers, which often contained multiple homogeneous processing cores. More complex scenarios like vision systems, ADAS and digital cockpits demand more sophisticated combinations of heterogeneous processing capabilities. As a result, today’s automotive SoCs contain multiple general-purpose central processing unit (CPU) cores and hard real-time CPU cores, along with graphics processing unit (GPU) cores, image signal processing (ISP) cores and neural processing unit (NPU) cores. Together, these units can perform artificial intelligence (AI) and machine learning (ML) functions much faster than traditional cores while using a fraction of the power. It is well known that Arm processor core IP provides a key enabler of automotive technology, with more than 90 percent of in-vehicle infotainment (IVI) systems and many under-the-hood applications powered by Arm-based chips, including meter cluster, HVAC control and side- or rear-view mirrors.

Perhaps less well known outside of the automotive design community is that Arteris system IP is used in over 70 percent of today’s automotive ADAS SoCs. All of the processor cores and other functions forming an SoC have to be connected together. Arteris FlexNoC® interconnect IP is used by the world’s top automotive semiconductor design teams as the backbone for their on-chip communications. Irrespective of whether the chip employs AMBA AXI3, AXI4, AHB, APB, OCP, PIF or a proprietary protocol, Arteris FlexNoC reduces the number of wires by nearly one-half, resulting in fewer gates and a more compact chip floor plan. One of the biggest problems with systems involving multiple processing cores is that each core maintains its own local cache of data and instructions and can share one or more caches with other cores. The term “cache coherence” refers to the process of ensuring that a coherent view of the data values is maintained in the multiple caches. To address this issue, the world’s top automotive semiconductor design teams employ Arteris Ncore® cache coherent interconnect IP, which is the industry’s only multi-protocol AMBA CHI and ACE cache coherent interconnect. Putting the Pedal to the Metal Arm and Arteris have been collaborating for many years, including Arteris supporting the deployment of Arm’s AMBA® 4 ACE™ specification in 2011, and Arm and Arteris giving joint presentations on Implementing ISO 26262 Compliant AI Systems with Arm and Arteris in 2018. This latter example described how AI and ML acceleration IP from Arm could be implemented in ISO 26262-compliant automotive systems with the help of functional safety mechanisms in the Arteris FlexNoC and Ncore interconnects. Now, in order to address the current automotive paradigm shift, Arm and Arteris are “putting the pedal to the metal” by extending their partnership to deliver best-in-class automotive solutions using Arm AE processors and Arteris interconnect IP, working towards aligning roadmaps more proactively to avoid surprises later in customer projects that integrate building blocks from both sources. As part of this collaboration, Arm has licensed a portfolio of released and future Arm Cortex CPUs to Arteris to expand and accelerate the delivery of solutions that will provide the most advanced safety and security capabilities to the automotive market. This new partnership means the two companies can fully align their roadmaps to deliver seamless integration that results in optimized flows for the best quality of results (QoR) and safety, all of which is key to delivering customer success. About Author Frank Schirrmeister is vice president of solutions and business development at Arteris. He leads activities in the automotive, data center, 5G/6G communications, mobile, aerospace and data center industry verticals and the technology horizontals artificial intelligence, machine learning and safety. Before Arteris, Frank held various senior leadership positions at Cadence Design Systems, Synopsys and Imperas, focusing on product marketing and management, solutions, strategic ecosystem partner initiatives and customer engagement. Category: SOC |

|

|

|||||

|

|

|||||

|

|||||