The semiconductor industry is witnessing an exciting breakthrough with the introduction of Veloce proFPGA CS, the first VP1902 FPGA-based software prototyping solution on the market. Beyond its remarkable architecture, modularity, scalability, and high performance, Veloce proFPGA CS sets itself apart by prioritizing the designers experience.

In this article, we explore Veloce proFPGA CS and its full visibility debug capabilities, driven by innovative and unique reconstruction algorithms. This functionality has redefined the way designers approach debugging. Additionally, we delve into the seamless integration of backdoor access for memories allowing quick experiments with different application scenarios.

In today’s era of rapidly advancing design complexity, traditional probe-based debugging methods are no longer sufficient. While probe-based debug may provide limited visibility to register signals, it lacks the granularity required for detailed analysis of all signals. This shortcoming hinders the ability to identify the root cause of bugs quickly and accurately.

And as designs become more intricate with hundreds of interconnected components, the need for a comprehensive view of the systems behavior has become critical. The innovative reconstruction algorithms offered by proFPGA CS enables visibility to the cause of bugs.

Unleashing Full Visibility:

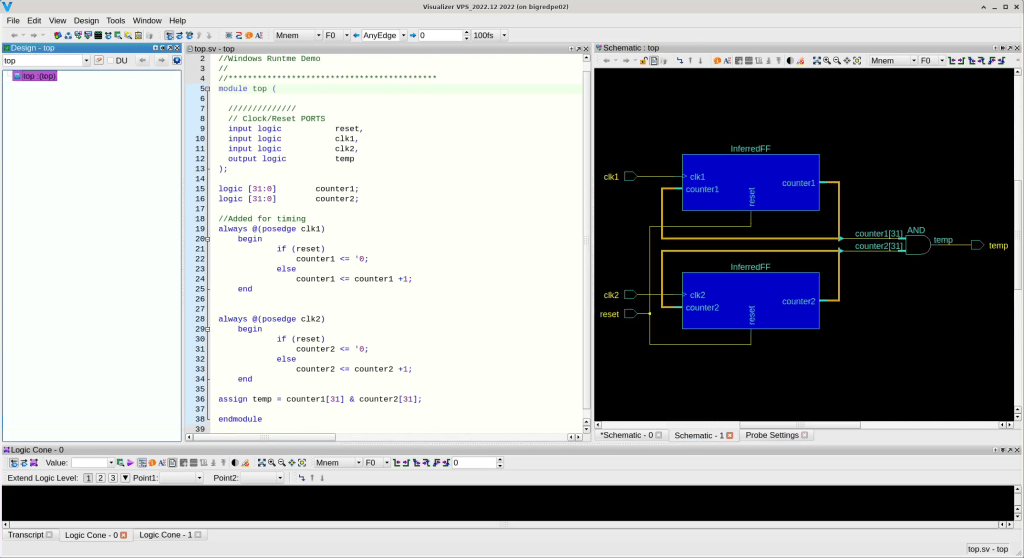

With Veloce proFPGA CS and the VPS user software for compile and debug, full visibility becomes a reality. Veloce proFPGA CS empowers designers to examine every aspect of their designs, from signals and registers to memories and combinatorial logic. This level of visibility provides an unprecedented understanding of system behavior.