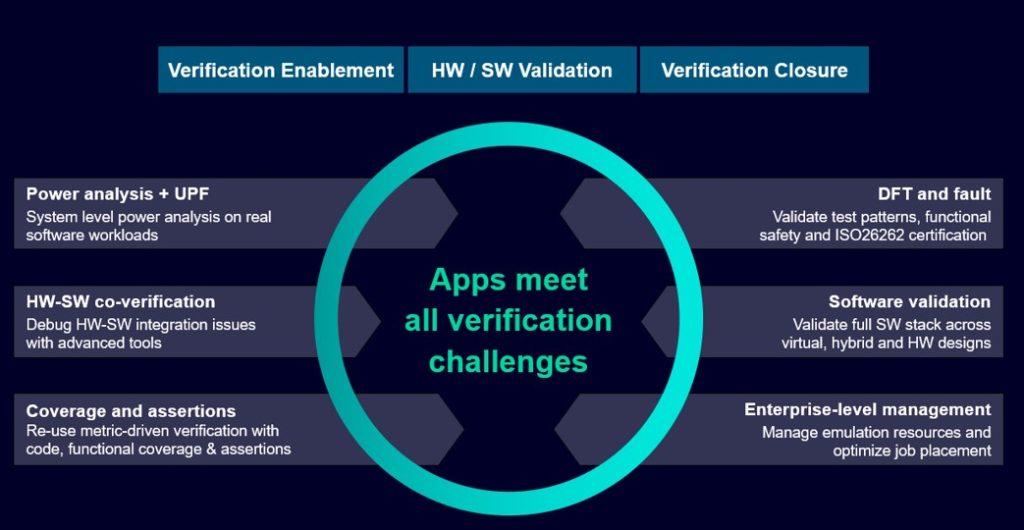

In the rapidly evolving semiconductor and electronic design world, hardware-assisted verification (HAV) has become an indispensable part of the design process. The use of hardware platforms like emulators and FPGA-based prototyping systems to enhance the verification and validation process, ensure designs meet their specifications efficiently and effectively. But what about the end users’ challenges and use cases? What tools and technologies are available to help enable a more efficient verification/validation environment or help with verification closure? What about teams who are tasked with HW/SW Co-verification tasks? Do they have the necessary tools and applications to get their job done? I think asking these critical questions and examining the use cases is important to providing a comprehensive solution that addresses the verification and validation team’s needs. To help understand how Siemens EDA is solving this challenge, let us delve into some key use cases of HAV, enabled by Veloce Apps.

Software development, debug, and validation

It is well known that Hardware-assisted verification plays a crucial role in software development, particularly in the initial stages of chip design. By using emulators, developers often run full workloads/software on hardware models, allowing them to identify and fix issues before the physical hardware is available. By providing full reference designs that operate stand-alone, or in a hybrid execution model with HAV platforms, one significantly accelerates the development cycle and reduces the risk of costly post-silicon bugs because system-level workloads were not run.