EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Andes’ vector processing; Cadence to acquire AWR; Synopsys’ die-to-die IP; GaN growth; Imagination’s new GPUsDecember 6th, 2019 by Roberto Frazzoli

Risc-V is making news this week, with the upcoming Risc-V Summit (December 10th to 12th in San Jose, CA) bringing several announcements regarding this open source ISA. Among the other recent news, some interesting updates concerning EDA, IP and power electronics. Andes adds Risc-V Vector instruction extension At the Risc-V Summit Andes will be unveiling details of its new AndesCore 27-series of CPU cores. The 27-series is the first licensable Risc-V core to deliver to a production licensee the Risc-V Vector instruction extension (RVV). The cores’ memory subsystem has also been re-architected to support the RVV requirements in terms of memory bandwidth and efficiency. The RVV is especially targeted to complex computation of large volume of matrix data required by emerging applications such as AI, AR/VR, computer vision, cryptography, and multimedia processing. According to Andes, the Risc-V Vector instruction extension differs from advanced SIMD architectures as it provides more flexibility, with scalable data sizes, flexible microarchitecture implementations, and a memory subsystem that can be optimized at the system level. One of the new cores, dubbed NX27V, contains a Vector Processing Unit (VPU) that allows an arbitrary vector length from 64-bit to 512-bit, and even 4096-bit by combining eight vector registers. Computation of integer, fixed point, floating point, and other AI-optimized representations can be any bit-width from 4 bits to 32 bits. Among other architectural innovations, the 27-series supports multiple outstanding memory accesses, so both the scalar and vector processors don’t have to wait for the data during cache misses. In addition, cache pre-fetches allow the memory to prepare data in advance of processor’s needs. Andes describes this new series as “ground-breaking”, claiming that its VPU has been “designed from the ground up to be a Cray-like full vectorization computation unit”, as opposed to “some advanced SIMD” offering only “incremental” performance growth over preexisting SIMD architectures. The 27-series processor beta release has been delivered to Andes’ first licensee in early December 2019; production database release is scheduled for Q1 2020. Initially available will be the 32-bit A27, the 64-bit AX27 (both tailored for applications running Linux) and the above-mentioned NX27V.

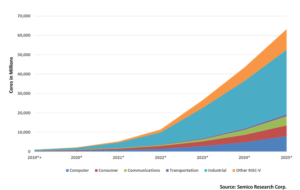

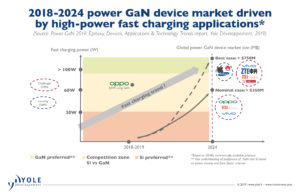

And according to Semico Research, the market will consume a total of 62.4 billion Risc-V CPU cores by 2025. This corresponds to a forecasted compound annual growth rate (CAGR) of 146.2 percent between 2018 and 2025. Growth will involve many market segments including computer, consumer, communication, transportation and industrial; the latter sector is forecasted to be the largest in terms of volume, with 16.7 billion cores by 2025. In terms of CAGR, though, Semico estimates that the communication sector will see the biggest growth due to the deployment of 5G. The report considers the fact that Risc-V application can range from one or two cores to more than 1000 cores in certain SoCs. Cadence to acquire AWR Based on a recent agreement, Cadence expects to acquire AWR – a subsidiary of National Instruments and an industry leader in high-frequency RF EDA. Cadence promises “a seamless integration” connecting the AWR Design Environment with several of its platforms. The flows resulting from the integration are also expected to be tightly connected with the National Instruments LabVIEW and PXI modular instrumentation systems, as part of a new strategic alliance. The collaboration is centered on the analog, mixed-signal and RF domains and on the Cadence Virtuoso and Spectre platforms, with physical data from the NI LabVIEW and PXI systems. Cadence and NI also plan to collaborate to define and build a common, connected flow enabling re-use of mixed-signal testbenches and stimulus from pre-silicon design verification to post-silicon validation and production test. Synopsys’s die-to-die IP With advanced SoCs for high-end data center and networking applications now reaching maximum reticle size limits, partitioning the design into smaller modular dies is often becoming a necessity. This is where die-to-die PHY IP comes into play. A few weeks ago, Cadence announced its IP for die-to-die connectivity in chiplet-based and System-in-Package devices targeted at high performance applications; now Synopsys is joining the race with its DesignWare Die-to-Die PHY IP. Targeted at a 7nm FinFET process, the new Synopsys IP focuses on ultra-short and extra-short reach connectivity in multi-chip modules for hyperscale data center, AI, and networking designs. Consuming less than one picojoule per bit, the die-to-die IP supports NRZ and PAM-4 signaling from 2.5G to 112G data rates. Its analog front-end enables links up to 50 millimeters for large multi-chip module designs. GaN goes mainstream According to market research firm Yole, gallium nitride is now entering mainstream consumer applications such as smartphone chargers. This marks a significant change, as in the last decade the GaN power market has been driven mostly by high-end, high performance applications requiring high-frequency switching, low on-resistance, and smaller size. A hint pointing at this new trend came a few weeks ago from a reverse engineering report performed by System Plus Consulting (part of the Yole group of companies), that discovered the use of GaN within an Anker’s wall charger. Yole is also reporting that Chinese smartphone maker Oppo has announced the adoption of a GaN HEMT (High Electron Mobility Transistor) device in its 65W inbox fast-chargers for its new Reno Ace flagship model, while in Q4 2019 Samsung has adopted a GaN HEMT device in its 45W accessory fast-chargers. Driven mainly by this kind of applications, Yole projects that the GaN power business will exceed US$350 million by 2024, with 85% CAGR between 2018 and 2024. Mobile gamers get new Imagination’s GPUs Even if described as “the GPU of everything”, the new IP from Imagination Technologies promises to make mobile gamers especially happy. Representing the tenth generation of the company’s PowerVR graphics architecture, the IMG A-Series is advertised as “the fastest GPU IP ever released”, with the flagship version reaching 2 TFLOPS. At the same clock and process, the new series offers 2.5x the performance, 8x faster machine learning processing and 60% lower power than current PowerVR devices shipping. Energy usage reduction has been achieved with a combination of techniques: tile-based deferred rendering, Pro-Active DVFS (Dynamic Voltage and Frequency Scaling) and Deadline Scheduling algorithms. If parts of the GPU aren’t fully utilized or needed for processing, they are immediately slowed down or even put to sleep. Lower power translates in a better experience for mobile gamers, as lower heat eliminates the need to reduce frame rate. The IMG A-Series includes four high-performance configurations and two versions for low-cost applications. |

|

|

|||||

|

|

|||||

|

|||||