EDACafe Editorial Roberto Frazzoli

Roberto Frazzoli is a contributing editor to EDACafe. His interests as a technology journalist focus on the semiconductor ecosystem in all its aspects. Roberto started covering electronics in 1987. His weekly contribution to EDACafe started in early 2019. Ansys to acquire LSTC; cloud-based EDA; voice recognition; copper vs fiber; carbon nanotube processors; and more weekly newsSeptember 12th, 2019 by Roberto Frazzoli

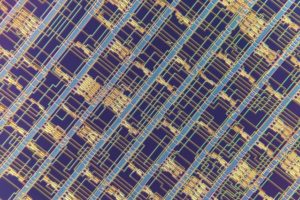

Carbon nanotubes are now a step closer to practical applications, thanks to an MIT research that was announced a couple of weeks ago. But first, a few industry news from the last few days. Let’s start with Ansys, that on September 11th unveiled an agreement to acquire Livermore Software Technology Corporation. The acquired company – LSTC for short – is the creator of LS-Dyna, a multiphysics solver widely adopted by the automotive industry to accurately predict a vehicle’s behavior and the effects on occupants during a collision. Verification in the cloud Synopsys has announced a collaboration with Google Cloud to provide a full end-to-end solution to perform functional verification workloads – with Synopsys VCS – in the cloud. Flexible hardware scalability offered in the cloud helps design teams to address peak/burst simulation capacity requirements, enabling a higher quality verification on a predictable schedule. The solution leverages the native Google Cloud-NetApp integration to bridge the on-premises and cloud infrastructures, together with tight integration between VCS and the Preemptible VM feature in Google Cloud. Low cost, low power voice command Voice control was one of the hot themes at the recent IFA consumer electronics show in Berlin. Germany. That’s where NXP launched an MCU-based solution for far-field voice control and command recognition that mainly addresses smart home and smart appliance products. The goal: enabling OEMs to add voice control without requiring cloud connectivity, thus removing privacy concerns and the need for Wi-Fi. The solution is built on NXP’s i.MX RT106L crossover MCU running FreeRTOS – to ensure low latency detection – and uses voice recognition technology from Snips (Paris, France). Digital signal processing capabilities for far-field operation are also embedded in the board. And right after IFA, QuickLogic unveiled it is partnering with Nuance Communications to deliver ultra-low power wake word and voice command technology for power-sensitive applications, including hearable and wearable devices. The Nuance voice recognition technology has been integrated with QuickLogic’s EOS Voice and Sensor Processing SoC. The solution specifically supports the Alexa wake word protocol and promises voice recognition accuracy even in noisy environments. Copper vs fiber optic Credo has announced the formation of the HiWire Consortium dedicated to the standardization and certification of a new category of Active Electrical Cables (AEC). Copper-based HiWire cables promise 400G deterministic and persistent connectivity for data centers at lower cost and power than Active Optical Cables (AOCs) for lengths up to 7m. HiWire cables integrate Forward error correction (FEC) and built-in retiming to ensure a fully equalized signal and ultra-low bit error rates. According to the consortium, HiWire cables are easy to connect to today’s most common switches, servers and storage. Founding members of the HiWire Consortium include Barefoot Networks, Credo, Dell EMC, Juniper Networks, Keysight and many more. Making satellite positioning more reliable with inertial data French research institute CEA-Leti and specialized company Orolia (also headquartered in France) have announced a new sensor-data-fusion engine that ensures resilient positioning and navigation even in cases of global navigation satellite system (GNSS) jamming or spoofing. According to CEA-Leti, the increasing reliance on a GNSS for transportation and for military operations requires positioning and navigation systems that can detect GNSS outages and provide resilient position and navigation features. Called FlexFusion, the algorithm technology processes data from GNSS, inertial management units (IMU) and odometers to provide precise positioning in all conditions. An IMU consists of triple-axis accelerometer, triple-axis gyrometer and triple-axis magnetometer. The new fusion approach exploits Bayesian estimators, e.g. Kalman filters. The data-fusion algorithm is performed locally to ensure that positioning and navigation information is failsafe even in case of jamming or spoofing of GNSS data. FlexFusion comes in two versions, with different CPU loads and resilience levels. Qualcomm to expand 5G offering Another hot topic at the above-mentioned IFA show was of course 5G. In Berlin, Qualcomm announced its plans to accelerate 5G global commercialization at scale by expanding its portfolio of 5G mobile platforms across the Snapdragon 8 Series, 7 Series and 6 Series in 2020. The Snapdragon 6 Series, in particular, targets the mobile experiences of “the masses”. Devices based on the Snapdragon 6 Series 5G Mobile Platform are expected to be commercially available in the second half of 2020, proliferating 5G globally. A RISC-V processor made of carbon nanotubes MIT researchers have built a 16-bit RISC-V microprocessor – consisting of more than 14,000 transistors – from carbon nanotubes, using regular semiconductor process technologies. To achieve this, the team addressed three key roadblocks. First, the researchers came up with a technique for dealing with the impurities that result in metallic behavior. The impact of metallic carbon nanotubes is different in the various parts of the circuit: it can be totally disruptive, or irrelevant. Running simulations to assess this impact on all the different standard cell combinations, the team was able to customize an EDA tool to automatically learn the combinations least likely to be affected by metallic carbon nanotubes. Thanks to this technique, the purity requirement was lowered from 99.999999 percent to 99.99 percent – a four orders of magnitude reduction that makes it possible to use carbon nanotubes manufactured with currently available technologies. As researchers observed, this allows “to buy carbon nanotubes off the shelf, drop them onto a wafer, and just build the circuit like normal, without doing anything else special.” The MIT researchers also found a way to build both PMOS and NMOS transistors out of carbon nanotubes, using a special process that involves platinum or titanium; this allowed the construction of a full CMOS structure. Lastly, they developed a technique for creating a uniform layer of single carbon nanotubes on the wafer, by removing unwanted bundles. The carbon nanotubes transistors (CNFETs) in this device have a channel length of roughly 1.5 micrometres; the processor clock frequency can reach 1 MHz. A complete description of this work has been published on the journal Nature. Upcoming events And speaking of RISC-V, a one-day conference specifically devoted to this architecture is in the list of the upcoming events. The “RISC-V CON” will take place in Santa Clara, CA, on October 15th, with speakers from Andes Technology, Faraday, Semico Research, AWS AI and Imperas. |

|

|

|||||

|

|

|||||

|

|||||