Posts Tagged ‘Automation’

Monday, January 31st, 2022

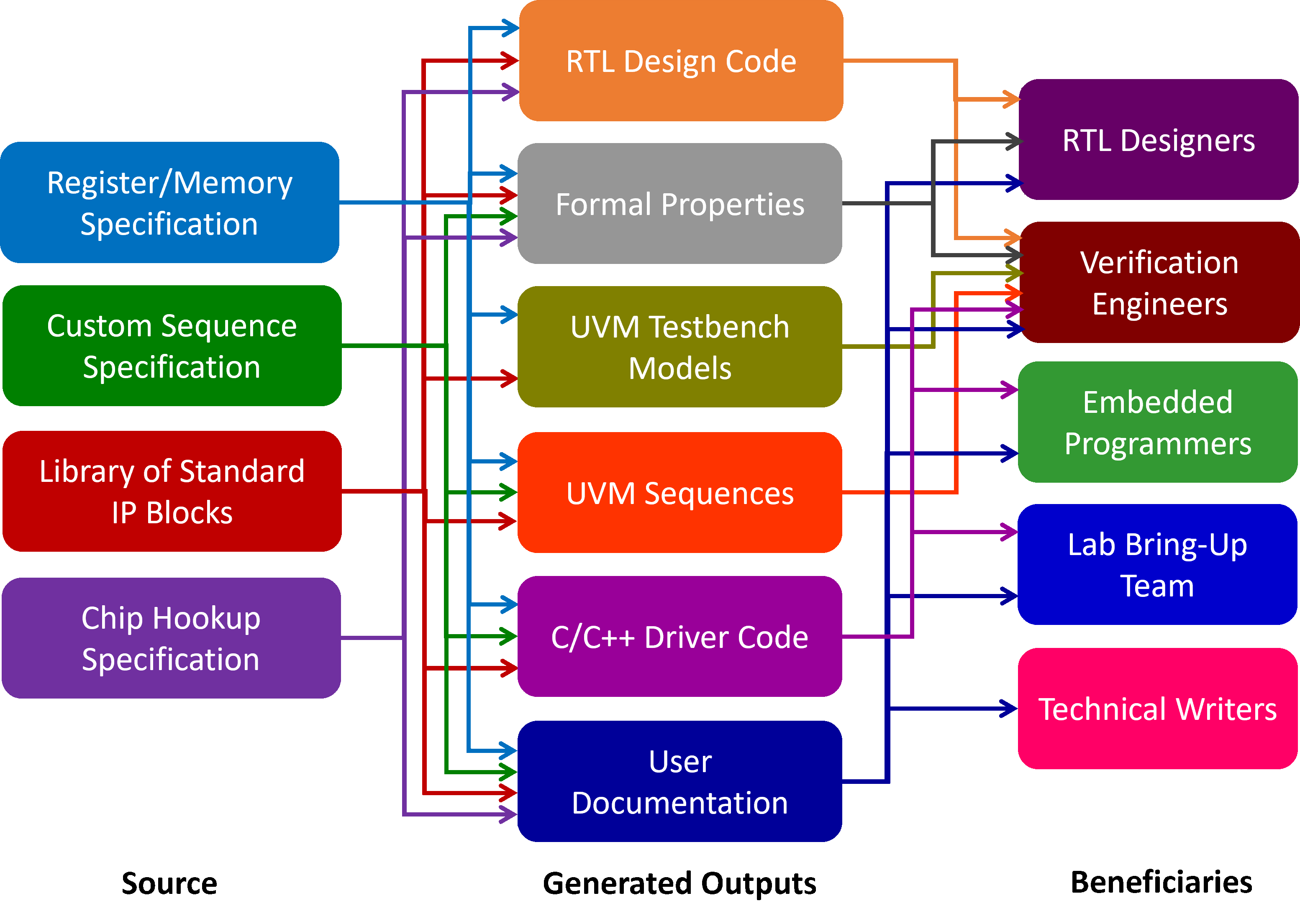

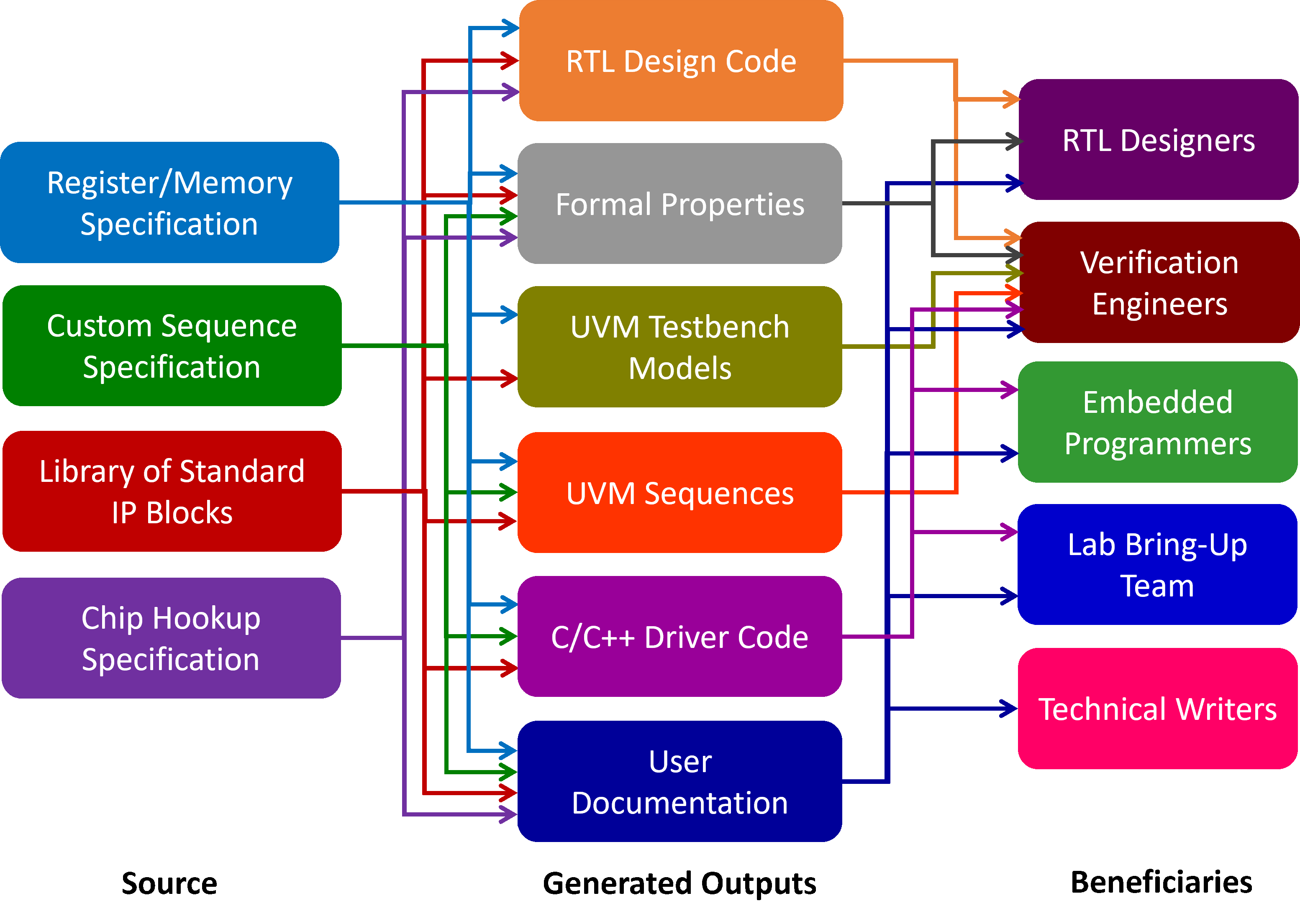

As an electronic design automation (EDA) company, Agnisys provides many benefits for chip design and verification engineers. Our specification automation solution generates both the register transfer level (RTL) design and key elements for verification with simulation and formal tools. As the diagram below shows, our solution also provides value to other teams. In this post, I’d like to focus specifically on embedded programmers, since we are seeing increasing interest in our capabilities in this domain.

By embedded programming, I mean just about any type of software that interacts directly with the hardware. This includes boot code, firmware, device drivers, and what is sometimes called hardware-dependent software (HdS). In a system-on-chip (SoC) device, these programs generally run on the embedded processors within the chip, but some parts may run on a host system as well. The key common element is that the software controls and communicates with the hardware by reading and writing a set of control and status registers (CSRs). Because we support register automation, we can facilitate embedded code development by generating the C/C++ header files for the registers in the design.

(more…)

Tags: Automation, Specification, SystemVerilog

No Comments »

Sunday, March 31st, 2019

As generations of designs evolved from a few hundred transistors to hundreds of billions, our industry abstracted the problem space from transistors to schematics to gates, and from RTL bit-level to transaction-level. Using abstraction, designers were able to focus on the high-level design and tests while the tools took care of the automation and calculations at the low-level – this certainly made the design flow more efficient and engineers more productive. Over the years abstraction has allowed the EDA industry to manage the ever-increasing complexity and scale of ASIC/SoC designs.

On a related note, check out Mark Glasser’s blog regarding his perspective on abstraction(while your there check out his great photography too).

The strategy behind the Portable Test and Stimulus Standard (PSS) is again to raise this level of abstraction to the next level. PSS will enable SoC teams specify stimulus and tests at a high-level. PSS has constructs for modeling high-level test scenarios such as data flow (buffer, streams, states), behavior (actions, activities, components, resource, pooling), constraints, randomization and coverage. The PSS tool generates the downstream code reusable from block, subsystem and system-level, which can be re-targeted for various verification platforms such as simulation, emulation, prototyping or post-silicon validation.

(more…)

Tags: Agnisys, Assertions, Automation, functional verification, hsi, IDesignSpec, ISequenceSpec, ISS, PSS, UVM registers, Verification

No Comments »

Tuesday, February 19th, 2019

By Louie De Luna, Agnisys Director of Sales and Marketing

Right after Google’s AlphaGo system defeated a human Go world champion in 2015, the hype of deep learning and machine learning (ML) was quickly assimilated into mainstream technology. In EDA, the application of ML algorithms actually dates back to 2008 – when two Machine Learning-related topics were presented at DAC. The first topic, Efficient System Design Space Exploration Using Machine Learning Techniques targeted design challenges and the second, Experiences and Advances in Formal and Dynamic Verification, targeted verification challenges.

As a company focused on solving both design and verification challenges associated to Hardware/Software Interface (HSI), Agnisys has extensive experience in register code generation and verification, so applying Machine Learning to register automation is a natural next step for us. Agnisys register tool IDesignSpec is a fully-matured solution with a large user base, where it can generate register code directly from the specification in Word, Excel, IP-XACT or SystemRDL. But in an ideal world, our users would rather use plain and simple English text to describe the register behavior rather than use special properties and syntax. Natural, plain English is still the hallmark of specifications in today’s system design and a lot of useful and actionable information is embedded in the natural language specification text.

(more…)

Tags: Agnisys, Automation, DVCon, Free register Generator, functional verification, hsi, IDesignSpec, Register Generator

No Comments »

|