Agnisys Automation Review Anupam Bakshi

Anupam Bakshi is Chief Executive Officer (CEO) for Agnisys, Inc., the pioneer and industry leader in Golden Executable Specification Solutions™. From his early days at Gateway Design Automation, through to his time at Cadence, PictureTel, and Avid Technology, he has been passionate about … More » Why DIY? Take Advantage of the Best Register Automation SolutionJanuary 11th, 2024 by Anupam Bakshi

Specification automation means the automatic generation of RTL design, verification, software, validation, and documentation files from executable specifications. That’s what we enable with our solutions at Agnisys. Specification automation begins with register automation. I mean that historically: registers were the first aspect of design that we tackled, and we were true pioneers of this technology. But it’s still true today: nearly everyone who takes advantage of our specification automation solutions starts with registers. Registers: The Fundamental ElementAs discussed in a recent post, registers are some of the most common and fundamental design elements. Literally everyone on a chip or intellectual property (IP) project can benefit from register automation. Your designs may contain hundreds of thousands of registers, and designing these by hand is clearly a painful task. Just typing in the register-transfer-level or RTL design code requires weeks or months of work. Like any hard coding, it’s highly susceptible to human error. Especially with many similarly named registers, typos are certain to occur.

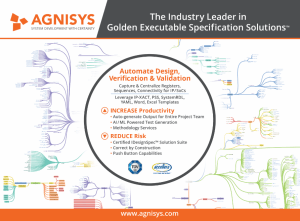

Chip developers realized this years ago, and many companies created scripts that would read spreadsheets or other forms of specifications and generate the register RTL automatically. Of course, this saves designer time at the beginning of a project, but the ongoing savings are even greater. Your specifications change many times over the course of a project for many reasons, and nearly all these updates have ripple effects on the registers. Manually updating register RTL again and again introduces more opportunities for errors to occur and consumes precious resources that should be spent on RTL design features that will differentiate your products. Electronic design automation (EDA) vendors saw register automation as a business opportunity, and a bunch of commercial tools became available. From this unruly mix, Agnisys emerged as the clear leader. We remain the leader today, with many companies worldwide using our solutions for register automation. You may wonder why this is so. Why don’t companies just write their own do-it-yourself (DIY) tools, use shareware programs, or select the partial solutions available from other vendors? I’d like to address that question. The True Cost of DIYOne lesson that all engineers learn is to focus on the areas where they can add value. Much as generating RTL code saves designer time for more important tasks, licensing EDA solutions saves programmer time for working on product features. Once upon a time, every chip company owned its own fab, packaged its own chips, wrote its own EDA tools, and more. Using commercial solutions saves time and resources, while enabling every user to benefit from the shared expertise of the entire industry as embodied in these solutions. It may seem attractive to write a register automation tool yourself, but the true cost of this path is always underestimated. Every piece of software requires an ongoing investment in maintenance and support. Internal tool teams in chip companies are necessary to develop makefiles, scripts, and “glue” programs that help automate the development flow. This is a limited-time effort that bears little resemblance to writing and supporting production software. If you do develop a DIY software automation tool for one project, without significant investment it becomes a throwaway effort. Each new project that wishes to use the tool will have new requirements, so the tool must evolve, and you need a team to evolve it. There are many formal and de facto standard formats and languages that must be supported for input, output, or both. These include everything from SystemRDL to IP-XACT, JSON, RALF, YAML, XML, comma-separated value (CSV), Microsoft Word, Microsoft Excel, and OpenOffice Calc. Further, new standards, and new versions of existing standards, emerge all the time. These also require ongoing tool development. It’s also easy to underestimate the costs of support. Chip companies often have internal help desks for information technology (IT) departments but answering questions about a chip development tool requires different skills. Users often need hands-on help to be successful, and they may benefit from tool training provided by register automation experts. An EDA vendor is in a much better position to provide training and support, including dedicated applications engineers, than an internal one-and-done tool team. Yes, all chips today require software. Your company likely has professional programming teams experienced in evolving and maintaining software while providing any necessary user support. But it makes much more sense to keep these teams focused on firmware and applications that are part of your products than on tools used only for internal hardware development. The Lacking Scope of DIYIt’s also important to know that most DIY, shareware, and commercial tools provide only a subset of what you really need for register automation. For example, there are hundreds of special register types in chips today, including indirect, indexed, read-only/write-only, alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, and read/write pairs. There are also many combinations of these types, as well as memories, that should all be handled by the register automation solution. More register types appear over time, yet another reason to avoid the ongoing investment required for a DIY tool. Generating just the registers isn’t enough. The automatically generated RTL must also include interfaces to standard buses such as APB, AHB, AHB-Lite, AXI4, AXI4-Lite, TileLink, Avalon, and Wishbone, plus support for proprietary buses. The register automation solution must generate clock-domain-crossing (CDC) structures when asynchronous clocks are present. The RTL must also include safety mechanisms such as parity, error-correcting codes (ECCs), cyclic redundancy checks (CRCs), and triple module redundancy (TMR) for safety-critical designs to meet the requirements of ISO 26262 and similar standards. Generating just the RTL isn’t enough. To verify the design, your team needs SystemVerilog register models, Register Model Generator, and testbenches based on the Universal Verification Methodology (UVM). Your programmers need C/C++ software sequences to read, write, and test your registers during pre-silicon verification in simulation and system validation in your bringup lab. Many of these sequences can be used by your programmers in their production drivers and embedded code as well. Finally, your technical writers need detailed register documentation in formats such as Microsoft Word, HTML, PDF, Markdown, and DITA. Therefore, a full register automation solution generates the RTL design, verification files, C/C++ code, and user-quality documentation automatically from the executable specification, to cater all the needs mentioned above. Whenever the spec changes, the push of a button updates all these files and keeps them consistent. Agnisys Efficient and Complete SolutionBy now, I hope that I’ve convinced you to choose a commercial register automation solution rather than developing your own DIY tool. But why Agnisys? The answer is simple. We have the most experience of any EDA vendor in this technology and we have a worldwide applications engineering team to enable your success. Our robust, proven solution supports every single one of the features and standards that I listed above as essential. Every member of your chip project team benefits directly from the files we generate. No other vendor can make this claim.

When you’re ready to move into other areas of specification automation beyond registers and memories, we’re ready for you. The Agnisys IDesignSpec Suite automates the design and verification of both standard and custom IP blocks as well as the hookup and assembly of these blocks into your complete chip. Please contact us to schedule a discussion or demonstration with a member of our team to see how you can benefit from the industry’s best register automation solution. Categories: Register Automation Solution, Registers |

|

|

|||||

|

|

|||||

|

|||||