Agnisys Automation Review Anupam Bakshi

Anupam Bakshi is Chief Executive Officer (CEO) for Agnisys, Inc., the pioneer and industry leader in Golden Executable Specification Solutions™. From his early days at Gateway Design Automation, through to his time at Cadence, PictureTel, and Avid Technology, he has been passionate about … More » Specifying Registers and Sequences with Portable StimulusNovember 6th, 2023 by Anupam Bakshi

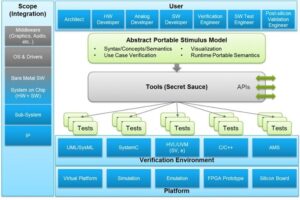

One of the most important things we do here at Agnisys is talk frequently to our users to keep track of what’s most important in the semiconductor industry. Technology is evolving constantly, industry alliances shift all the time, and the only thing constant is change. We use what we learn to make many key decisions on developing new products, adding new features to existing products, and to develop comprehensive solutions for specific user groups and vertical markets. For example, as discussed in a recent post, we found that SystemRDL is less widely adopted than IP-XCAT and so smooth translation from one to the other is a key capability that we offer. Portable Stimulus is on the RiseMore recently, we have seen a significant uptick of interest in the Portable Stimulus Standard (PSS) developed by Accellera. The first version was released in June 2018, and PSS 2.1 was announced just a few weeks ago. Key electronic design automation (EDA) companies and semiconductor developers continue to work on evolving the standard and educating engineers on how to use it successfully on real-work projects. Agnisys is proud to be a member of the PSS working group and one of several established EDA vendors with products supporting the standard. One way to view PSS is as the next step beyond the Universal Verification Methodology (UVM), which was also developed as a standard by Accellera. UVM made it much easier to reuse intellectual property (IP) designs between projects without having to rework the entire verification environment (testbench and tests). However, UVM focuses purely on SystemVerilog-based simulation and is not applicable to other verification and validation platforms. It also provides limited support across multiple levels of hierarchy, such as leveraging standalone IP testbenches at the subsystem or full-chip level. PSS was created to address both these limitations. It enables the specification of verification intent and the automatic generation of tests that work “vertically” from block to system and “horizontally” from simulation to silicon. Figure 1 is a graphical view of this portability developed by Accellera. EDA tools read an abstract PSS model and generate tests for the selected level of hierarchy and target platform. These tests can be in multiple languages and formats. For example, SystemVerilog tests run in UVM testbenches and C/C++ tests run in simulation as well as on actual silicon in the bringup lab.  Figure 1: Accellera view of portable stimulus

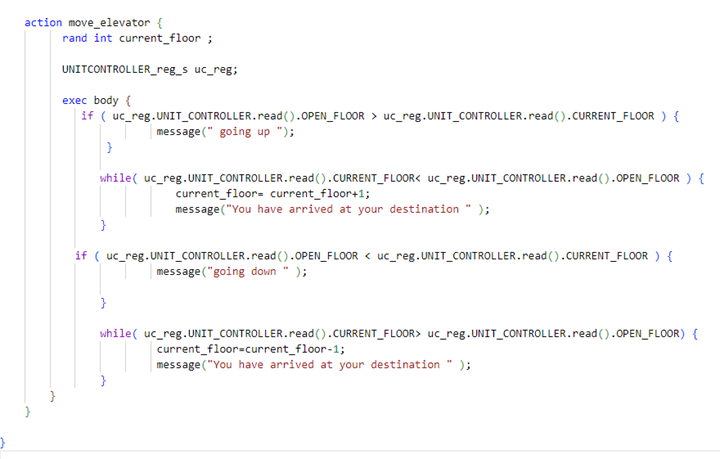

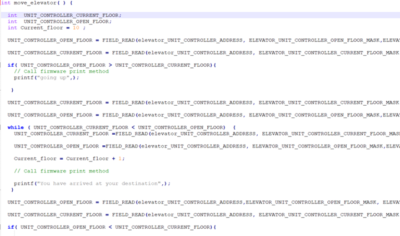

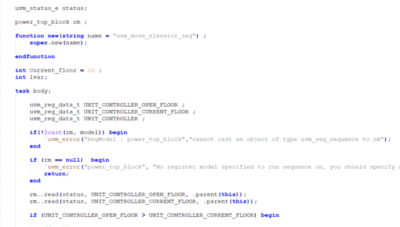

PSS for Registers and SequencesThe capabilities of PSS are quite broad, and many are not relevant to the specification automation space where we operate. One key area of overlap is the specification of the architecturally visible registers in an IP or chip design and the sequences that configure and program these registers. When a design is reset, most of the registers and some types of memories require initialization and configuration to bring the design to a known operational state. Additional programming sequences are required during runtime operation of the design to enable its mission functionality. Historically, the relevant sequences must be specified independently by each team for each hierarchical level and verification or validation platform. The IP team creates standalone SystemVerilog sequences, and these need to be modified by the chip verification team. Programmers write their sequences in C/C++ so that they can run on embedded or host processors. Naturally, there is a high likelihood that these multiple sequences don’t match entirely, requiring significant time and resources to find and fix the inconsistencies during verification and validation. This undesirable process is repeated over and over as the register definitions evolve over the course of the project. Every change introduces new opportunities for divergent and unsynchronized sequences. PSS 2.1 addresses this dilemma by enabling the definition of registers and sequences in an abstract and portable way. EDA tools can then generate the sequences specifically for each level of hierarchy and each platform, ensuring that they are all in agreement. This automated process is repeated every time that the registers change, ensuring that all register programming tests remain in sync. Each IP team specifies its registers and sequences, and engineers working at higher levels of the design hierarchy can simply generate appropriate tests without having to know details or change the specifications. Clearly, this yields big savings in project time and cost. Agnisys and PSS: A Great CombinationOur IDesignSpec™ Suite specification automation solution is perfectly positioned to leverage the advantages of PSS. There are two key aspects of our support. First, our IDS-Validate can generate register models and programming sequences in PSS code. You have many options for register and sequence specification in our solution, and you have the option of having us generate PSS outputs. If you don’t happen to use PSS, we also directly generate SystemVerilog and C/C++ tests for specific platforms. Figure 2 shows an example of automatically generated PSS code.  Figure 2: PSS Input Code We also support the option of specifying your registers and sequences yourself in PSS code. In this case, IDS-Validate can read in your PSS model and generate all desired output files. We offer an intelligent PSS editor to help you write your models. If you have a mix of register and sequence definitions in PSS and other formats, we can merge them together in our output tests. Figures 3 and 4 show an example of PSS input code and automatically generated C/C++ and SystemVerilog/UVM tests.  Figure 3: C Output Code generated by IDS-Validate  Figure 4: UVM output code generated by IDS-Validate With PSS emerging as a major force in IP and system-on-chip (SoC) verification, we have invested in the technology to read and generate portable stimulus models. This allows our users to interact with PSS solutions from other vendors and to leverage this state-of-the-art standard. We would love to tell you more about a solution, arrange a demo, and provide an evaluation license when you’re ready to try it out. Please contact us anytime! Category: PSS |

|

|

|||||

|

|

|||||

|

|||||