One of the most important things we do here at Agnisys is talk frequently to our users to keep track of what’s most important in the semiconductor industry. Technology is evolving constantly, industry alliances shift all the time, and the only thing constant is change. We use what we learn to make many key decisions on developing new products, adding new features to existing products, and to develop comprehensive solutions for specific user groups and vertical markets. For example, as discussed in a recent post, we found that SystemRDL is less widely adopted than IP-XCAT and so smooth translation from one to the other is a key capability that we offer.

Portable Stimulus is on the Rise

More recently, we have seen a significant uptick of interest in the Portable Stimulus Standard (PSS) developed by Accellera. The first version was released in June 2018, and PSS 2.1 was announced just a few weeks ago. Key electronic design automation (EDA) companies and semiconductor developers continue to work on evolving the standard and educating engineers on how to use it successfully on real-work projects. Agnisys is proud to be a member of the PSS working group and one of several established EDA vendors with products supporting the standard.

One way to view PSS is as the next step beyond the Universal Verification Methodology (UVM), which was also developed as a standard by Accellera. UVM made it much easier to reuse intellectual property (IP) designs between projects without having to rework the entire verification environment (testbench and tests). However, UVM focuses purely on SystemVerilog-based simulation and is not applicable to other verification and validation platforms. It also provides limited support across multiple levels of hierarchy, such as leveraging standalone IP testbenches at the subsystem or full-chip level.

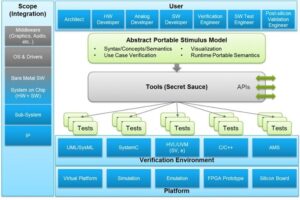

PSS was created to address both these limitations. It enables the specification of verification intent and the automatic generation of tests that work “vertically” from block to system and “horizontally” from simulation to silicon. Figure 1 is a graphical view of this portability developed by Accellera. EDA tools read an abstract PSS model and generate tests for the selected level of hierarchy and target platform. These tests can be in multiple languages and formats. For example, SystemVerilog tests run in UVM testbenches and C/C++ tests run in simulation as well as on actual silicon in the bringup lab.

Figure 1: Accellera view of portable stimulus