Agnisys Automation Review Louie De Luna

Louie is the Director of Marketing and Sales at Agnisys, Inc. He has over 15 years of experience in FPGAs, ASICs and EDA industries. Louie was most recently the Director of Marketing for Aldec where he was instrumental in the development and execution of the strategy for the entire functional verification solutions. He received his B.S. in Computer Engineering from University of Las Vegas, NV in 2001. « Less Louie De Luna

Louie is the Director of Marketing and Sales at Agnisys, Inc. He has over 15 years of experience in FPGAs, ASICs and EDA industries. Louie was most recently the Director of Marketing for Aldec where he was instrumental in the development and execution of the strategy for the entire functional … More » Not your Average UVM Testbench Generator – Unveiling at DAC 2019May 20th, 2019 by Louie De Luna

Being so immersed in the work and technology, it’s easy to forget where we are in this technological revolution. Some of us didn’t really appreciate the impact of the internet until we held it in our hands and swiped to the next pages of seemingly infinite information. In the last decade, we saw how the automotive industry converted most of their mechanical systems into electronics and added Advanced Driving Assistance Systems (ADAS) for the safety of the passengers and other vehicles. We saw how home automation has transformed our daily life with the help of Automatic Speech Recognition (ASR) and low-power wireless technology. The next decade ahead is even more exciting as new generation of SoCs will power new artificial intelligence (AI) applications that will touch human lives and transform various industries across the board. For sure, the associated design and verification challenges and cost will only increase, and that’s why the EDA community has been preparing for it with the help of standards from Accellera such as UVM and now PSS. As a company focused on design/verification of critical aspects of SoCs, we understand our place and know our role. Our goal is two-fold: automate verification and minimize functional flaws. At this year’s Design Automation Conference (DAC) in Las Vegas NV, we will showcase our most innovative solution yet that is built on top of our core code-generation technology. We call it Specta-AV™ – a massive UVM testbench generator that automates verification and minimizes functional flaws that originate from errors or changes in the spec. UVM has been good and useful to us, and will continue to do so in the coming decade. But UVM is notorious for two main problems: its steep learning curve and the staggering amount of UVM code required to verify a full SoC. Verifying a custom IP with one master and slave agent requires tens of thousands of lines of UVM code. Verifying a full SoC requires multi-million lines of UVM code (in addition to the array of standard VIPs). Automating the process of creating UVM code is critical, and is a great solution to these two problems.

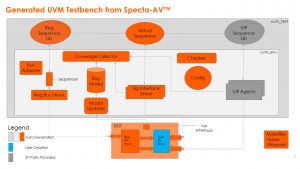

With Specta-AV, the generation of the complete UVM testbench architecture including sequence items, configurations, checkers, coverage and even the plumbing within UVM are all automated – and not just for registers but also for custom IPs! Its core engine comes from our flagship product IDesignSpec™ that can parse hierarchical register specifications in IP-XACT, SystemRDL, Word, Excel or YAML, and generate register RTL, UVM model and C Header. Specta-AV generates code from a golden specification which can synchronize all design and verification activities. Changes in the specification only requires re-generation of the code which prevents any disconnect between SoC groups that can be a culprit of SoC functional flaws and project delays.

The tool flow consists of three main basic parts:

Additionally, we’re also presenting our latest complementary solutions at DAC that automate verification and minimize SoC functional flaws, and they are as follows: Cloud-Based Code Generator for Registers and Sequences Yes! We are taking IDS NextGen™ to the cloud. This will revolutionize how the files are managed: no hassles in managing local files, no issues with storage and no local software installation required for the product. IDS NextGen handles individual IP to sub-system to SoC level, and is compatible with registers specs in Word, Excel, IP-XACT, RALF, CSV or System RDL. It generates design and verification code for not just registers but also sequences in a single integrated environment compatible with Windows, Linux or MAC. It reduces creation of sequences by having the user define sequences in pseudo-code and generate the sequence code in either SystemVerilog or C. IDS NextGen in the cloud will enable the teams to collaborate online with secure cloud servers from AWS™ or Azure™. The team can access the data accessible from anywhere, from any device. Support for RISC-V TileLink Bus Protocol New generation SoCs such as those for machine learning applications require new types of processor architecture, and the open-source RISC-V ISA is picking up a lot of steam. Moore’s Law has ended and standard CPUs are not able to meet the performance and power requirements of new generation SoCs. Domain-specific architectures with the help of open-source concept will play a critical role to push innovations forward. TileLink is an open-source bus-protocol with low latency and cache-coherent shared memory designed for RISC-V, and it’s now supported in IDesignSpec. Sequences in Python or NLP-based Sequence Detection We now have come to a point where we can pick sequence of operations from a functional specification and create meaningful code from it. Many power users of our sequence generator tool ISequenceSpec™ wanted to enter sequences in simple text independent of other tools (Word, Excel or Calc). They wanted their sequences easy and simple to make with a quick turnaround without any applications consuming too much CPU and memory resource. The sequences are entered as pseudo-code, and from there users can re-target into SystemVerilog for simulation, C for firmware tests and CSV for post-silicon validation tests. In an ideal world, some of our users don’t want to even capture sequences in pseudo-code (even though it’s really easy!). Their biggest pain is to understand the spec in order to create the required sequences. They want a Neural Language Processor (NLP) algorithm to parse the spec and auto-generate the sequences. This is really a hard problem to solve, but we have started the initial phase. Using the NLP algorithm we can parse a spec in Word and generate sequences in C or SystemVerilog. Vertical Reuse of Registers and Sequences Register design and verification at the IP-level can be straightforward, but painful challenges start to creep up as the IPs are integrated into the subsystem and the final system. In this presentation we will discuss various verification and firmware use cases that are common. We will discuss the underlying challenges and demonstrate best-practices on how to reuse the auto-generated register RTL, UVM model, UVM test environment and configuration/test sequences at subsystem and final system. Most importantly, we will show specific features in IDesignSpec and ISequenceSpec that enable vertical reuse. Register Design for Low-Power In order for IoT devices to become as ubiquitous as we have envisioned it to be, low-power is one of the main requirements. IDesignSpec now supports the following features for low power RTL design:

As the EDA community braces for the upcoming design/verification challenges brought upon by new applications in AI, autonomous cars, 5G, IoT and cloud computing – as a company it’s good to know our place and focus. It’s good to know that we are contributing value and where we stand during this technological revolution. I invite you to come visit us at DAC at Booth#812, and see our presentations all throughout the day. Don’t forget to visit our coffee bar while you’re there and take our Design/Verification Quiz to win a wireless charger -we’re giving six wireless chargers this year. See you in Vegas! Tags: Agnisys, dac, Design and Verification, Embedded, Free register Generator, UVM, UVM registers Categories: Registers, Testbench Generator This entry was posted on Monday, May 20th, 2019 at 10:23 pm. You can follow any responses to this entry through the RSS 2.0 feed. You can leave a response, or trackback from your own site. |

|

|||||

|

|

|||||

|

|||||